DFx(Design for X)作为系统性设计方法论,通过整合可制造性(DFM)、可装配性(DFA)、可测试性(DFT)等全生命周期要素,为工程师提供了一套从设计到量产的优化框架。

一、可制造性设计(DFM):

DFM是DFx体系的核心,直接影响PCB打样的良率与成本。其核心原则包括:

-

工艺边界适配:设计需匹配PCB厂商的加工能力,例如线宽/线距需≥3mil(0.075mm),避免因超限导致蚀刻缺陷。拼板设计需遵循标准尺寸(如200mm×250mm),并通过工艺边(≥4.5mm宽)提升传送稳定性。

-

材料与表面处理优化:高频场景选用低损耗基材(如Rogers 4350B),表面处理优先选择沉金或OSP工艺,平衡成本与可靠性。对于0.4mm间距BGA,需采用开窗工艺避免焊接空洞。

-

阻抗控制与信号完整性:通过SI9000仿真验证关键信号阻抗,微带线厚度误差控制在±10%,确保毫米波频段信号完整性。

二、可装配性设计(DFA):自动化生产的保障

DFA聚焦于降低装配复杂度,提升直通率:

-

元器件布局规范:0201以下封装器件需间隔≥0.2mm,避免贴片偏移;连接器引脚需外伸设计,便于返修。双面贴装时,优先采用正正拼板,减少钢网切换次数。

-

定位与公差控制:设置3个拼板MARK点(对角分布),定位孔中心距板边≥5mm。关键焊盘公差需控制在±0.05mm,防止BGA锡球虚焊。

-

模块化设计:将电源模块、射频模块独立成板,通过连接器互联,缩短单板调试周期。

三、可测试性设计(DFT):质量管控的早期介入

DFT通过设计冗余提升测试效率:

-

测试点布局:关键网络(如电源、时钟)需预留测试焊盘,间距≥0.4mm。高速信号线需避免在过孔处设置测试点,防止信号反射。

-

边界扫描与飞线检测:对高密度板采用JTAG边界扫描,替代传统飞线检测。在盲埋孔区域增加辅助检测孔,提升开路/短路检出率。

-

电源完整性验证:在打样阶段进行PDN仿真,确保去耦电容布局满足纹波要求(<50mV),避免量产时因电源噪声导致功能异常。

四、全生命周期协同:从打样到量产的闭环

DFx的价值在于打通设计、制造、服务链路:

-

环保性设计(DFE):优先选用无卤素基材(如BT树脂),减少卤化物对环境的污染。通过物料标准化(如0805封装替代0603),降低供应链复杂度。

-

可服务性设计(DFS):在PCB边缘预留维修缺口(≥2mm),关键器件标注维修坐标。对多层板采用激光通孔技术,减少维修时钻孔损伤。

-

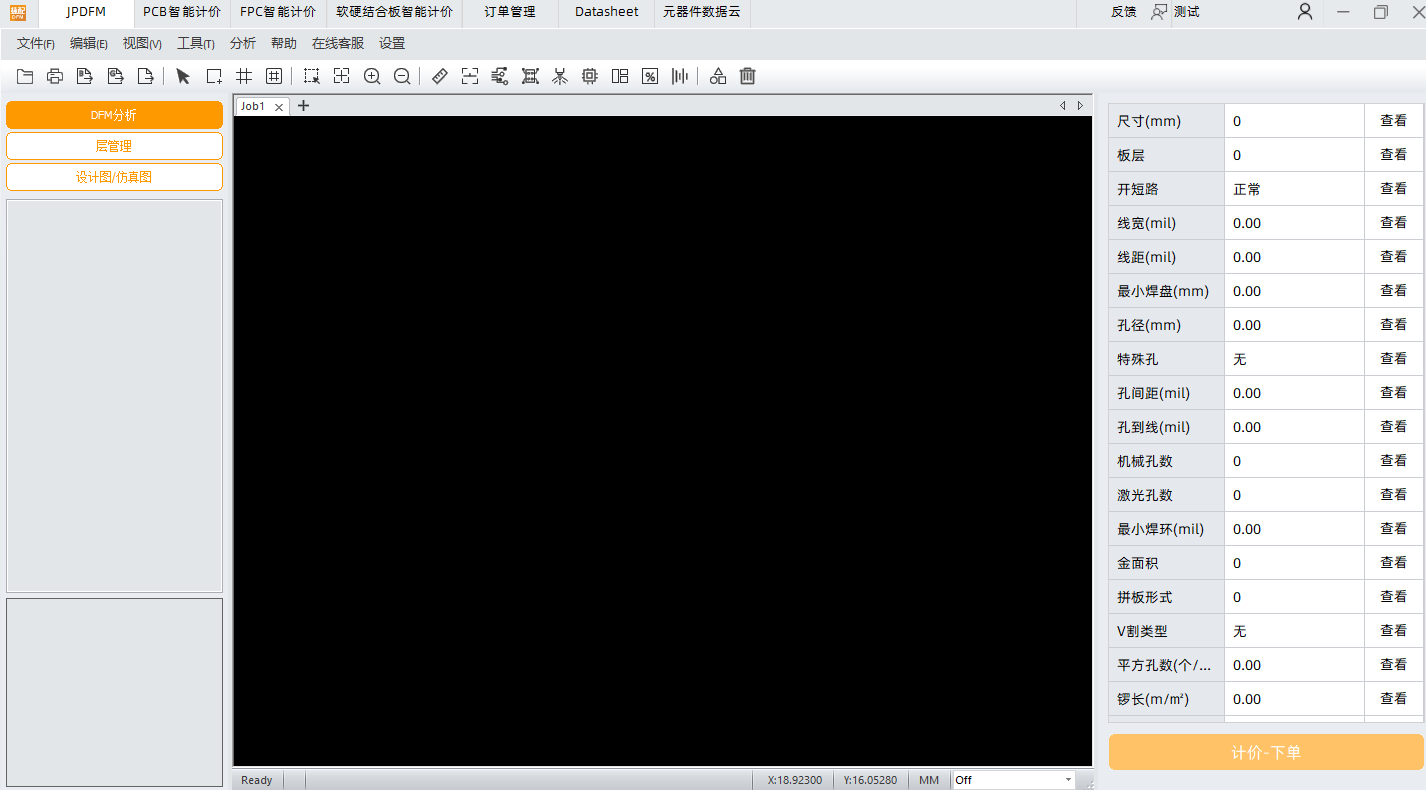

数据协同工具:采用Vayo-DFX系统集成Gerber、BOM数据,自动审查3000+条工艺规则,提前发现设计冲突,缩短打样迭代周期。

PCB打样中的DFx实践需围绕三大核心:

-

工艺适配:从线宽到拼板尺寸严格匹配厂商能力

-

自动化友好:通过模块化与标准化降低装配复杂度

-

数据驱动:利用仿真与审查工具实现设计-制造闭环

PCB打样中的DFx策略解析

PCB打样中的DFx策略解析

738

738

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?