在高速电子领域,精心设计的 6 层 PCB 叠层是确保信号完整性和性能的支柱。无论您是在从事电信、计算还是高级消费电子产品,优化 6 层 PCB 叠层以实现阻抗控制、串扰最小化和高速布线都可以决定您的设计的成败。

为什么 6 层 PCB 叠层对高速设计很重要

6 层 PCB 叠层在复杂性和成本之间实现了平衡,使其成为需要多个信号层、配电和接地层的设计的热门选择。与简单的 2 层或 4 层板不同,6 层配置提供了足够的空间来分离高速信号、减少电磁干扰 (EMI) 并保持受控阻抗。这对于 USB 3.0、HDMI 或 DDR 内存接口等信号速度通常超过 1 GHz 的应用至关重要。

6 层叠层的主要目标是确保信号完整性,这是指信号从源传输到目的地而不失真、丢失或干扰的能力。不良的叠层设计可能会导致串扰、信号反射或 EMI 等问题,所有这些都会降低性能。通过仔细规划信号层、电源层和接地层的布置,您可以最大限度地降低这些风险并实现稳定、高性能的设计。

设计用于阻抗控制的 6 层 PCB 叠层

阻抗控制是高速设计的基石,尤其是在信号走线经常彼此靠近的 6 层 PCB 中。受控阻抗可确保信号传输时没有反射,当走线阻抗和连接的组件之间不匹配时,可能会发生反射。对于高速信号,单端走线的公共目标阻抗为 50 欧姆,差分对的公共目标阻抗为 100 欧姆。

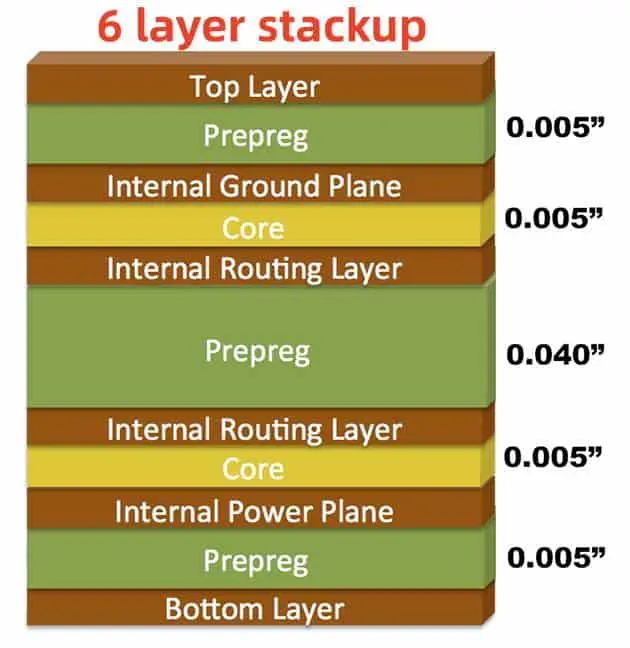

要实现 6 层 PCB 叠层阻抗控制,首先要定义层排列。典型的 6 层叠层可能如下所示:

-

第 1 层:用于高速走线的顶部信号层

-

第 2 层:接地层

-

第 3 层:电源平面

-

第 4 层:电源平面或附加接地

-

第 5 层:接地层

-

第 6 层:底部信号层

这种配置将接地层放置在信号层附近,以提供一致的阻抗参考并降低EMI。信号层与其相邻接地层之间的距离以及介电材料的特性决定了走线阻抗。例如,在介电常数 (Dk) 为 4.2 的 1.6 mm 厚电路板上,走线宽度为 5 密耳 (0.127 毫米),当距接地层 0.2 毫米时,可能会产生 50 欧姆阻抗。使用阻抗计算器或模拟工具根据您的特定电路板材料和厚度微调这些值。

保持叠层的对称性也至关重要。不平衡的叠层可能会在制造过程中导致翘曲,从而导致信号完整性问题。确保层之间的介电厚度一致,并咨询您的制造合作伙伴以验证可制造性。

6 层 PCB 信号完整性的材料选择

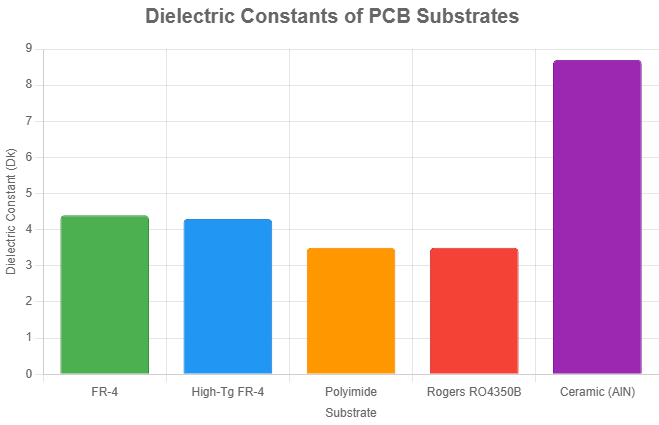

材料的选择在保持信号完整性方面起着重要作用,特别是对于高速设计。在关注信号完整性的 6 层 PCB 材料选择时,需要考虑的两个关键因素是基板材料的介电常数 (Dk) 和耗散因数 (Df)。

标准 FR-4 材料的 Dk 约为 4.2 至 4.5,适用于许多应用,但由于其较高的 Df(约 0.02),可能会在 1 GHz 以上的频率下引入信号损失。对于在 5 GHz 或更高频率下运行的高速设计,请考虑使用 Isola 370HR(Dk ~3.9,Df ~0.009)或 Rogers RO4350B(Dk ~3.5,Df ~0.0037)等低损耗材料。这些材料最大限度地减少了信号衰减,并确保高频信号具有更好的性能。

此外,还要注意铜箔类型。由于集肤效应,粗糙的铜表面会增加高频下的信号损耗,即电流在导体表面附近流动。选择更光滑的铜箔,例如轧制退火 (RA) 铜,以减少关键信号路径中的损耗。

层间的介电厚度也会影响阻抗和串扰。更薄的电介质(例如 0.1 mm)允许信号层和接地层之间更紧密的耦合,改善阻抗控制,但增加制造成本。通过选择满足设计频率和速度要求的材料和厚度,平衡性能与预算。

6 层 PCB 的高速布线指南

在 6 层 PCB 上布线高速信号需要仔细规划以避免干扰并保持信号质量。遵循 6 层 PCB 高速布线指南可以显着提高设计性能。以下是一些实用技巧:

-

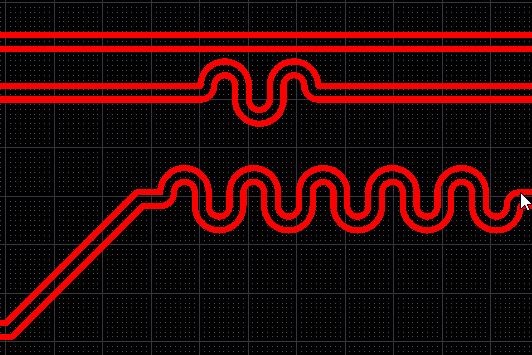

最小化走线长度:保持高速信号走线尽可能短,以减少延迟和信号丢失。例如,在 10 Gbps 信号中,1 英寸(25.4 mm)走线可能会引入明显的传播延迟(约 150 ps)。

-

避免尖角:使用 45 度角或弯曲走线而不是 90 度弯曲,以防止阻抗不连续性引起的信号反射。

-

将差分对布线在一起:对于 USB 或以太网等差分信号,请保持对的走线平行且长度匹配在 5 密耳(0.127 毫米)以内,以避免偏斜。

-

隔离高速信号:将高速走线放置在接地层附近的外层,并避免将它们布线在电源或接地层的分叉上,因为这会中断返回路径并导致 EMI。

-

使用通过缝合:在高速信号过孔附近添加接地过孔,以提供低阻抗返回路径并减少串扰。

层分配也很重要。将顶层和底层保留用于高速信号和敏感模拟走线,同时使用内层用于配电或较慢的数字信号。这种分离减少了干扰,并使关键信号靠近其参考平面。

6 层 PCB 的信号完整性仿真

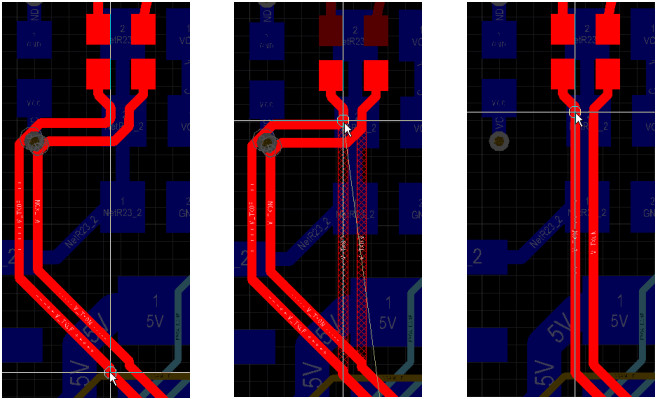

在将设计发送进行制造之前,必须执行 6 层 PCB 信号完整性仿真,以识别反射、串扰或时序错误等潜在问题。仿真工具允许您对叠层、跟踪几何形状和材料属性进行建模,以预测信号在实际条件下的行为方式。

首先模拟关键走线的阻抗。工具可以根据走线的宽度、厚度和与接地层的接近程度来计算走线的特性阻抗。例如,仿真可能会显示 0.2 毫米电介质上的 6 密耳宽走线可实现 50 欧姆阻抗,从而帮助您在需要时调整尺寸。

接下来,运行时域反射计 (TDR) 仿真以检测信号路径沿的阻抗失配。这可以突出显示导致反射的过孔存根或终止不良的走线等问题。此外,对高速数字信号执行眼图分析,以确保在 5 Gbps 或更高的数据速率下有足够的电压裕度和时序窗口。

6 层 PCB 的串扰最小化技术

串扰是相邻走线之间信号的不必要耦合,是高速设计中的常见挑战。实施 6 层 PCB 串扰最小化技术可以显着提高信号质量。以下是减少串扰的行之有效的策略:

-

增加迹线间距:在相邻高速走线之间保持至少 3 倍走线宽度的间距。对于 5 mil 走线,这意味着 15 mil 的间隔以最大限度地减少耦合。

-

使用接地层作为屏蔽:在与连续接地层相邻的层上布线高速信号。接地层充当屏蔽层,吸收杂散电磁场。

-

在不同层上路由信号:如果间距有限,则将攻击者和受害者走线布线在不同层上,并在它们之间放置一个接地层以阻挡干扰。

-

最小化并行运行:避免高速走线的长时间并行运行,因为它们会增加串扰的机会。如果不可避免,请将平行部分的长度保持在 500 密耳(12.7 毫米)以下。

-

添加防护跟踪:在关键信号之间放置接地保护走线,以将它们彼此隔离。使用过孔将这些走线在多个点接地。

串扰还受到信号上升时间的影响。更快的上升时间(例如,低于 100 ps)会增加耦合的可能性,因此如果性能允许,请考虑减慢边缘速度。仿真工具可以帮助量化串扰水平并指导对走线间距或层分配的调整。

成功 6 层 PCB 设计的实用技巧

除了技术方面之外,一些实际考虑因素可以确保您的 6 层 PCB 设计从概念到生产都取得成功:

-

尽早与制造商合作:与您的制造合作伙伴分享您的叠层和材料选择,以确认它们能够满足走线宽度、介电厚度和阻抗控制的公差。

-

测试原型:构建和测试原型以验证仿真。使用矢量网络分析仪 (VNA) 测量关键路径上的阻抗和信号损耗。

-

文档设计规则:在设计软件中明确定义走线宽度、间距和过孔尺寸等设计约束,以避免布局过程中出现错误。

-

热管理计划:高速设计通常会产生热量,因此请采用热通孔并确保电源平面能够有效散热。

通过将这些实践集成到您的工作流程中,您将创建一个 6 层 PCB,它不仅满足性能目标,而且保持可制造性和成本效益。

掌握 6 层 PCB 叠层以实现高速成功

为高速应用设计 6 层 PCB 叠层是一项复杂但有益的任务。通过专注于阻抗控制、材料选择、布线指南、信号完整性模拟和串扰最小化,您可以构建即使在数千兆位速度下也能提供卓越性能的电路板。每一层、走线和材料选择都有助于整体信号质量,因此对细节的关注至关重要。

479

479

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?