四层PCB与运算放大器的结合能显著提升电路性能。但设计不当反而会引入噪声、振荡等问题。

一、层叠结构:

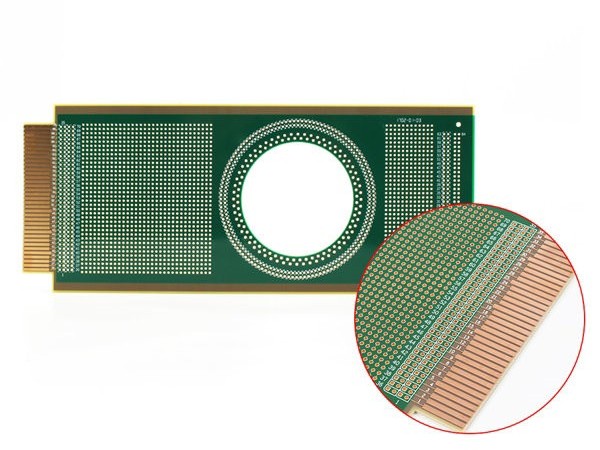

四层PCB的标准层叠通常采用两种方案:

-

方案A(信号-GND-PWR-信号):顶层和底层走信号线,中间两层分别作为完整的地平面和电源平面。这种结构为运放提供了低阻抗回流路径,可将电源噪声降低40%以上。

-

方案B(GND-信号-PWR-信号):将地平面置于顶层下方,适合高频电路。地平面能屏蔽外部干扰,但需注意内层信号线的跨分割风险。

关键细节:工程师应保持地平面完整。避免在接地层开槽,否则会使回流路径绕行,增大环路电感。某音频采集板测试显示,地平面开槽导致50Hz工频噪声增加6dB。

二、电源设计:抑制噪声的核心策略

旁路电容布局决定生死:

-

在运放电源引脚3mm范围内,工程师必须放置0.1μF陶瓷电容。该电容需采用0805或更小封装,以降低等效串联电感(ESL)。

-

距离电源引脚5-8mm处,工程师应增加10μF钽电容,用于抑制低频纹波。电容接地端需直接连接地平面过孔,避免通过长走线接地。

案例教训:某心电图仪最初将电容置于背面,电源引脚通过过孔连接。这增加了1.2nH电感,导致运放自激振荡。优化为同层布局后问题消失。

三、信号链路:

反相输入端(IN-)是敏感点:

-

IN-引脚具有高输入阻抗(通常>1GΩ)。工程师应将其走线长度控制在5mm内。每增加1mm走线,引入约0.3pF寄生电容,可能导致相位裕度下降20°。

-

反馈电阻必须紧贴IN-引脚。某光电检测电路中,反馈电阻距离过远引入2pF电容,造成100kHz以上频段增益异常波动。

差分走线规则:

-

对高速运放(如GBW>100MHz),工程师需采用阻抗匹配设计。例如USB差分对应保持100Ω±5%阻抗,线宽/间距按5/7mil(微带线)或4/9mil(带状线)设计。

-

避免信号线平行走线。两线间距小于3倍线宽时,串扰增加15dB。工程师可用接地铜箔隔离敏感信号。

四、热管理与可制造性

散热过孔阵列的应用:

-

功率运放(如TPA6120)需在PCB底部增加散热焊盘。工程师应在焊盘下方打6×6阵列过孔(孔径0.3mm),连接至地平面散热。这可使结温降低18℃。

-

避免将电解电容靠近散热源。某电源模块中,电容距电感5mm导致寿命从8000小时缩短至2000小时。

DFM(可制造性设计)要点:

-

贴片元件统一0°方向排列,减少贴片机旋转时间,提升良率30%。

-

BGA封装运放(如OPA2182)角落预留0.1mm×0.1mm禁布区,防止应力断裂焊球。

五、验证闭环:

TDR阻抗实测不可替代:

-

工程师需对关键走线进行时域反射计(TDR)测试。某雷达板设计时仿真阻抗50Ω,实测因铜厚偏差导致阻抗升至58Ω,引发信号反射。调整线宽后解决。

电磁场仿真预判风险:

-

使用CST或HyperLynx分析辐射热点。某电机驱动板仿真发现运放输出线与MOSFET栅极耦合,通过增加5mm间距使干扰降低12dB。

四层PCB上的运放设计本质是空间、电源与信号的三角平衡:中间层构建低噪声供电源,表层走线需在有限空间内规避寄生效应。优秀设计如同精密钟表——接地平面是支撑机芯的基板,电源旁路像擒纵机构滤除能量波动,而信号路径则是齿轮组,每个齿距(阻抗)的误差都将导致系统失准。当理论计算完结时,真正的工程才刚刚开始:用示波器验证每一毫伏的偏差,用热像仪追踪每一摄氏度的异常,最终在实验室与仿真的鸿沟上架起可量产的桥梁。

四层PCB运算放大器设计要点解析

四层PCB运算放大器设计要点解析

637

637

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?