在快节奏的电子世界中,多层 PCB 是高性能设备的支柱。但是,如何确保设计中的多层 PCB 信号完整性呢?

信号完整性对于多层 PCB 至关重要,可以防止数据错误、延迟和性能问题。通过掌握受控阻抗多层 PCB 设计和多层 PCB 中的串扰减少等概念,您可以创建可靠、高效的电路板。让我们探讨优化设计以实现最佳性能的关键原则、最佳实践和可行技巧。

多层 PCB 由由绝缘层隔开的多层导电材料组成,可实现紧凑而复杂的电路设计。这些电路板在从智能手机到工业设备的现代电子产品中至关重要,因为它们能够处理高密度连接和复杂的布线。

然而,随着层数和速度的提高,保持多层 PCB 信号完整性成为一项挑战。信号完整性是指电信号通过 PCB 时的质量。信号完整性差会导致数据损坏、时序错误和电磁干扰 (EMI)。对于高速多层 PCB 设计,确保信号完整性对于满足性能标准并避免昂贵的重新设计是不容谈判的。

多层PCB信号完整性的主要挑战

设计多层 PCB 以实现最佳信号完整性需要解决多项挑战。让我们分解一下最常见的问题及其对性能的影响。

1. 多层PCB中的信号丢失

当信号在通过电路板时减弱时,就会发生多层 PCB 中的信号丢失,这通常是由于高频下的电阻、介电损耗或集肤效应造成的。这种损耗会降低性能,特别是在信号以千兆赫兹频率运行的高速应用中。

2. 多层PCB中的串扰

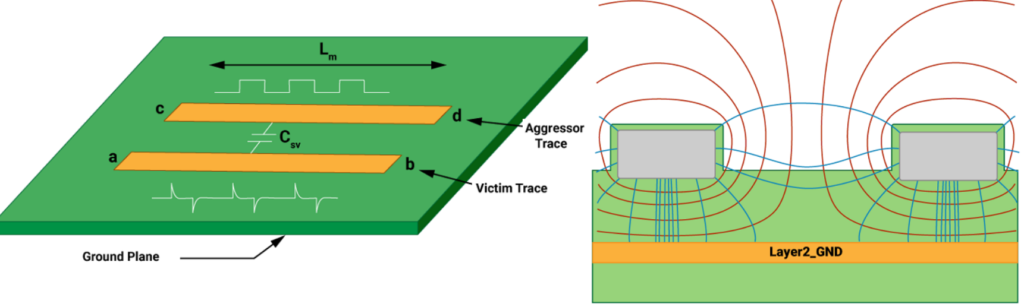

当相邻走线上的信号相互干扰时,就会发生串扰,从而导致噪声和数据错误。在多层板中,紧密的间距和平行走线增加了多层PCB中减少串扰的风险成为当务之急。

为了对抗串扰,请在高速信号之间保持走线宽度的最小间距为 3 倍。在信号层之间使用接地层也可以充当屏蔽层,减少电磁耦合。例如,与没有专用接地层的设计相比,具有专用接地层的 4 层 PCB 可以减少高达 30% 的串扰。

3. 阻抗失配

在受控阻抗多层 PCB 设计中,保持一致的阻抗对于信号完整性至关重要。阻抗失配会导致反射,导致信号失真。对于 USB 3.0 等高速信号,90 欧姆差分的目标阻抗很常见,超过 ±10% 的偏差可能会导致严重问题。

在设计过程中使用阻抗计算器,将走线宽度、间距和介电厚度与所需值相匹配。叠层规划,即信号层放置在靠近参考平面的位置,有助于实现对阻抗的更严格控制。

高速多层 PCB 设计的最佳实践

高速多层 PCB 设计的设计需要关注布局、材料选择和布线技术。以下是确保项目信号完整性的行之有效的策略。

1. 优化 PCB 叠层以提高信号完整性

多层 PCB 中的层排列(称为叠层)对信号质量起着至关重要的作用。精心规划的叠层可最大限度地减少噪声并支持受控阻抗。

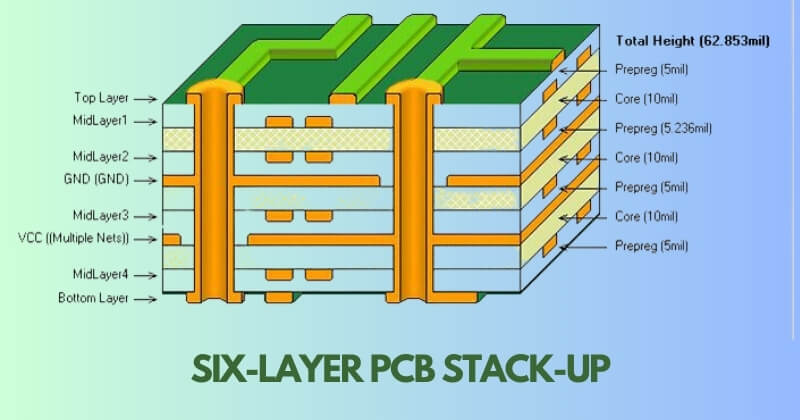

对于 6 层 PCB,常见的叠层可能是:

-

第 1 层:顶部信号

-

第 2 层:接地层

-

第 3 层:内部信号

-

第 4 层:电源平面

-

第 5 层:接地层

-

第 6 层:底部信号

将接地层放置在信号层附近可提供低阻抗返回路径,从而降低EMI。将高速信号保持在外层或参考平面附近,以将阻抗控制在目标值的 ±5% 以内。

2. 使用受控阻抗技术

对于受控阻抗多层 PCB 设计,精确的走线几何形状和介电性能至关重要。高速信号,例如 DDR4 内存中的信号(以 3200 MT/s 运行),通常需要单端走线的特性阻抗为 50 欧姆。

3. 通过材料选择最大限度地减少信号损失

选择正确的材料可以显着减少多层 PCB 设计中的信号损失。标准 FR-4 材料具有更高的损耗角正切(约 0.02),这会降低频率高于 1 GHz 的信号。相反,选择损耗角正切低于 0.005 的高级层压板以获得更好的性能。

此外,考虑使用低粗糙度的铜箔,以最大限度地减少蒙皮效应损失。这些材料虽然价格较高,但可以在高频设计中的长走线上将信号幅度提高多达 15%。

4. 实施减少串扰策略

有效减少多层 PCB 中的串扰涉及布局和布线技术。避免长距离并行高速走线。如果不可避免,请增加间距或在它们之间插入接地走线以充当屏障。

在 10 层板中,将内层专用于接地层和电源层,以隔离信号层。这种方法可以将串扰引起的噪声降低多达 40%,确保密集设计中的信号更清晰。

多层PCB信号完整性的高级技巧

除了基础知识之外,使用先进技术微调您的设计可以进一步提高性能。这些技巧对于从事尖端应用的工程师特别有用。

1. 明智地使用过孔存根

在多层板中,过孔连接层与层之间的走线,但长过孔短截线可以充当天线,引起反射。背钻是一种去除未使用的过孔短截线的过程,在运行速度高于 10 Gbps 的高速设计中,可以减少高达 25% 的信号反射。

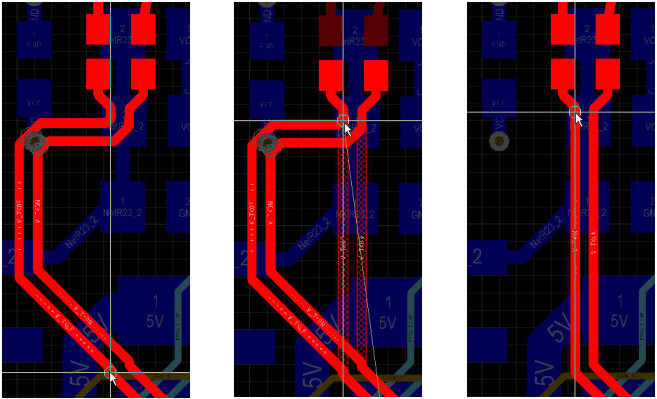

2. 实现差分对路由

对于 PCIe 或 HDMI 等高速信号,差分对很常见。以相等的长度和一致的间距布线这些对,以保持信号时序。仅 5 密耳(0.127 毫米)的失配可能会引入偏斜,从而导致速度高于 5 Gbps 时的数据错误。

3. 仿真和测试设计

在制造之前,使用仿真软件对信号行为进行建模。工具可以预测阻抗失配、串扰和信号丢失,从而允许您调整设计。使用时域反射计 (TDR) 进行制造后测试可以验证 ±5% 精度内的阻抗值。

多层PCB设计中要避免的常见错误

即使是经验丰富的工程师也会忽略关键细节。以下是关注多层 PCB 信号完整性时需要避免的陷阱。

-

忽略接地层:跳过连续接地层会中断返回路径,增加 EMI 和信号噪声。

-

重载层:在单层上布线过多的高速信号会导致串扰和阻抗问题。

-

忽略材料规格:使用标准材料进行高频设计通常会导致多层 PCB 中信号损失过大。

构建更好的多层 PCB

掌握多层 PCB 信号完整性是创建可靠、高性能电子产品的游戏规则改变者。通过专注于高速多层 PCB 设计、解决多层 PCB 中的信号损失以及优先减少多层 PCB 中的串扰,您可以克服常见挑战并提供卓越的结果。

544

544

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?