一、并联电阻的作用

在某些方案里,晶振并联 1MΩ 电阻时程序能正常运行,若无此电阻,程序会出现滞后甚至无法运行的情况。这背后的原因值得探究。

(一)原因剖析

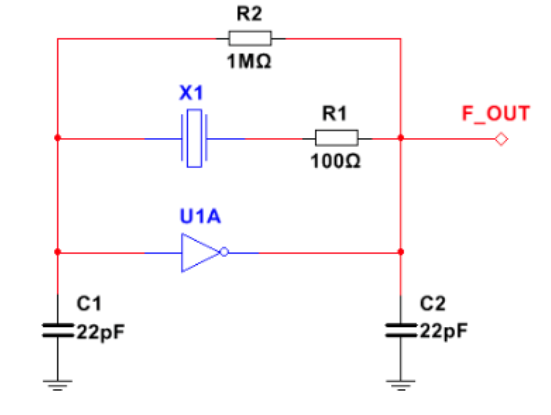

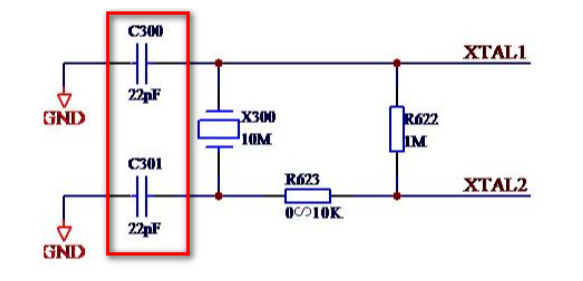

在无源晶振的应用方案中,两个外接电容的主要功能是微调晶振产生的时钟频率。而并联 1MΩ 电阻的关键作用在于助力晶振起振。当程序出现启动缓慢或无法运行的状况时,并联 1MΩ 电阻往往是有效的解决办法。

这个 1MΩ 电阻的原理在于,它能使原本作为逻辑反相器的器件工作在线性区,从而获得增益。因为反相器在饱和区是没有增益的,而没有增益的条件下,晶振是无法起振的。简单来说,并联 1MΩ 电阻增加了电路中的负性阻抗(-R),提升了增益,进而缩短了晶振的起振时间,让晶振更容易起振。

从另一个角度来讲,假设电路中没有任何扰动信号,晶振是无法起振的。在实际的反相门电路中,很多电路不加这个电阻也能起振,这是因为一般的电路都存在扰动信号。然而,有部分反相门电路如果不加这个电阻就无法起振,原因在于扰动信号的强度不足。

另外,在低温环境下,振荡电路的阻抗也会发生变化。当阻抗增加到一定程度时,晶振就会面临起振困难或不起振的问题。此时,并联 1MΩ 电阻就显得尤为必要。为了进一步增强振荡电路的稳定性,建议同时给晶振串联一个 100Ω 的电阻,这样能够有效减少晶振的频率偏移程度。

需要注意的是,并联电阻不能过小,串联电阻也不能过大。否则,在温度较低的情况下,电路就不易起振。

二、负载电容与外接电容的区分

在实际应用中,常常有人将晶振的负载电容与外接电容混淆,甚至误认为这是相同的参数,这种想法是完全错误的。

(一)负载电容

负载电容是晶振的一个内部重要电气参数。对于功耗不太敏感的电子设备 PCBA,常见的晶振负载电容有 15PF、18PF、20PF。而对于像腕表、手机、蓝牙耳机这类对低功耗有较高需求的电子产品,PCBA 上通常会采用负载电容较小的晶振,例如 6PF、7PF、9PF、10PF、12PF。晶振的负载电容在生产过程中已经根据需求通过加工工艺确定,在应用中是无法更改的。

(二)外接电容

外接电容是指在 PCBA 板上分别与晶振频率输入脚与输出脚串联的电子元件。其值的大小由晶振负载电容与电路板杂散电容(包括 IC 电容在内)共同决定,通常是这两者的总和。

在振荡电路的应用中,晶振负载电容、杂散电容与外接电容之间的关系如下:CL 代表石英晶体谐振器的负载电容,CS 指的是杂散电容,涵盖了 IC 内部的杂散容值、电路板布线间的电容量以及 PCB 板各层之间的寄生电容等,C1 和 C2 则分别是石英晶体谐振器在电路应用中的两颗外接电容。

外接电容的应用主要有两个目的。其一是针对晶振频率进行微调,使其尽可能接近目标频率。遵循的规则是,外接电容越大,晶振输出频率越偏负向;反之,外接电容越小,晶振输出频率则趋于正向变化。其二是起到对振荡电路的稳定作用,这也是建议在晶振频率输入脚与输出脚分别加一颗同值电容的原因。

最后需要提醒两点:一是外接电容的作用仅限于对晶振频率进行微调。如果晶振工作时频偏过大,那就需要考虑晶振本身精度的问题,比如是否需要将晶振精度提升,以满足芯片的要求。二是外接电容仅用于无源晶振的应用,在有源晶振的电路应用中,无需外接电容。

总之,正确理解和处理晶振电路中的并联电阻以及负载电容与外接电容的问题,对于确保电子电路的稳定、可靠运行至关重要。

744

744

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?