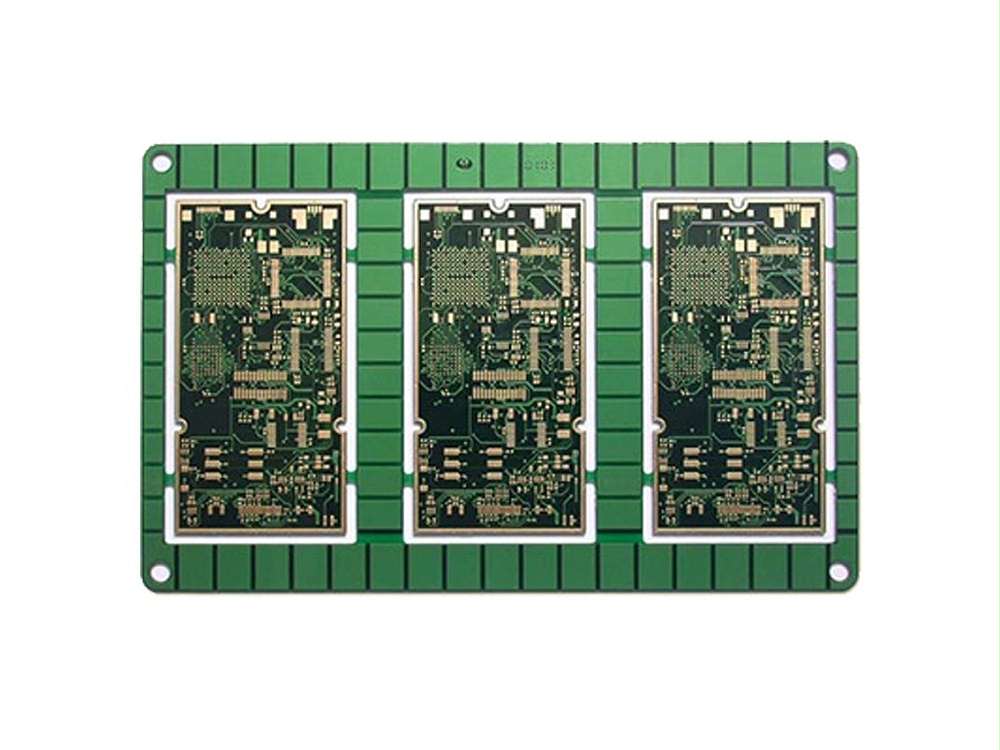

一组长度偏差仅6mil的DDR数据线——这相当于人类头发直径的十分之一,这场微观世界的毫米级战争,正是六层PCB设计中长度匹配与蛇形走线的终极博弈。

一、六层架构:长度匹配的“电磁战场”

黄金堆叠法则决定长度匹配的成败:

-

最优方案:信号层(GND)-信号层(PWR)-信号层(GND)对称结构

-

核心机密:第3层(内层信号)是最佳蛇形绕线层,其地平面屏蔽使串扰降低40%

-

致命陷阱:假八层结构(六层板模拟八层)会导致阻抗突变±8Ω,直接吞噬±5mil长度容限

层间耦合的隐形规则:

当差分对跨越电源分割区时,需在分割两侧放置0.1μF+10μF电容组成“π型滤波器”,否则回流路径断裂将引发等效长度偏差达22mil。

二、蛇形走线:±5mil精度的微观手术

蛇形线参数生死线(以5mil线宽为例):

参数安全值危险阈值失效后果振幅(L)25-75mil>100mil阻抗突变15%间隙(S)≥15mil<12mil串扰增加30dB转角半径≥7.5mil<5mil信号反射率飙升40%平行长度≤3倍线宽>5倍线宽延时误差超±8mil

三、科学真相:蛇形线的三大认知颠覆

误区破除:

-

“蛇形线抗干扰”:实验证明,5GHz信号经蛇形线后噪声容限下降20%,其本质是时序补偿工具而非滤波器

-

“任意角度绕线”:30°斜角蛇形线比90°直角损耗低14%,但45°才是加工精度与性能的平衡点

-

“等长即同步”:在28Gbps高速链路中,±5mil长度匹配仅解决60%时序问题,还需相位容限窗控制(±1.5ps抖动)

量子级操作指南:

-

使用梯度绕线法:从PHY芯片向外振幅递增(15mil→50mil),避免集中谐振

-

带状线优先原则:内层蛇形线比微带线延时偏差小0.7ps/inch,尤其适用于DDR4-3200

-

添加地线护城河:蛇形线两侧布置0.2mm宽接地铜带,串扰抑制比提升18dB

设计启示:当6G向太赫兹频段进军,±5mil误差容限正在崩塌。某实验室数据显示:在140GHz频段,1mil长度偏差会导致相位偏移11°——这意味着,今天的精度极限只是明天的起点。而那些在铜箔上蜿蜒的蛇形线,终将成为电子文明史上的“机械钟摆”,被量子级同步技术永久封存。

品质科普附录:蛇形线为何产生串扰?

电磁耦合原理:

当信号在平行蛇形线段传输时,会形成“差分天线”结构

人眼类比:

如同人眼无法分辨0.1mm间距的双线(视为单一线条),高速信号也会将紧密平行的蛇形线误判为合并路径,导致能量泄漏——这恰是串扰的微观真相。

193

193

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?