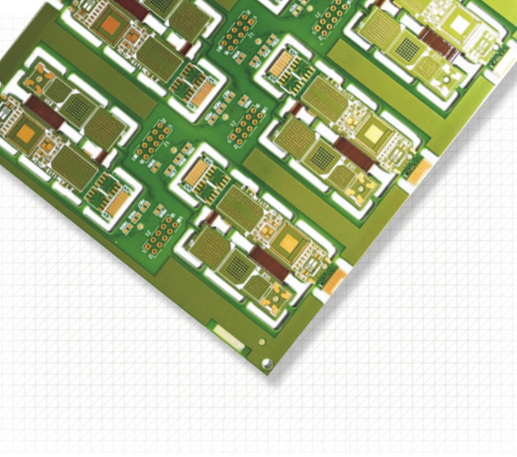

大尺寸 PCB 板的布线长度常达 0.5-1m(如服务器的 PCIe 4.0 布线、工业控制柜的电源回路),远超过小尺寸 PCB 的 10cm 极限 —— 长距离布线会导致信号衰减(1m 高速信号衰减 3dB)、时序偏移(时钟信号时序差超 100ps)、串扰加剧(-25dB),若设计不当,会导致设备功能失效(如服务器数据传输误码率 10⁻⁶)。大尺寸 PCB 的布线设计需围绕 “高速信号损耗补偿、时序同步、电源分配、接地优化” 四大核心,结合信号特性与设备需求,制定针对性策略,确保信号完整性。今天,我们解析布线设计的关键技术,结合参数与案例,帮你实现长距离布线的信号稳定。

一、高速信号布线:损耗补偿与阻抗控制

大尺寸 PCB 的高速信号(如 PCIe 4.0、DDR5、10Gbps 以太网)需重点解决 “传输损耗” 与 “阻抗匹配”,避免信号失真。

1. 传输损耗补偿

-

损耗类型与应对:

-

导体损耗(占比 40%):因趋肤效应,高频电流集中在铜箔表面,可选用 “高光滑铜箔”(粗糙度 Ra≤0.1μm),导体损耗减少 20%;

-

介质损耗(占比 50%):基材的 tanδ 越大,损耗越高,10Gbps 信号在普通 FR-4(tanδ=0.02)中 1m 损耗 3dB,在高頻基材(如罗杰斯 4350B,tanδ=0.0037)中损耗 1.2dB,可根据频率选择基材;

-

辐射损耗(占比 10%):通过 “屏蔽布线”(信号线两侧加接地铜箔,宽度≥0.5mm)减少辐射,损耗降低 15%;

-

中继器与均衡器:1m 以上的高速信号(如 PCIe 4.0)需在中间添加 “信号中继器”(如 TI 的 DS100BR410)或 “均衡器”(如 ADI 的 AD8129),补偿 3dB 损耗,误码率从 10⁻⁶降至 10⁻¹²。

2. 阻抗精准控制

-

线宽与基材匹配:根据基材参数计算线宽,例如罗杰斯 4350B(εr=3.48,厚度 0.508mm)的 50Ω 微带线,1oz 铜箔线宽 0.82mm,2oz 铜箔 0.78mm,线宽公差需控制在 ±0.01mm;

-

过孔阻抗补偿:大尺寸 PCB 的高速信号常需跨层,过孔的寄生电感(≈1nH)会导致阻抗突变,需在过孔旁加 “接地过孔”(间距≤0.3mm),并采用 “背钻” 工艺去除过孔的无用部分,寄生电感降至 0.3nH,阻抗偏差≤5%;

-

阻抗仿真验证:布线前用 Ansys SIwave 仿真全链路阻抗(从发送端到接收端),确保阻抗波动≤±10%,例如 1m 长的 DDR5 布线,仿真后阻抗波动 8%,满足要求。

二、时序同步:解决长距离布线时差

大尺寸 PCB 的多通道高速信号(如 DDR5 的 8 通道、PCIe 的 4 通道)需保证 “时序同步”,若通道间时序差超 50ps,会导致数据采样错误,需通过 “等长布线” 与 “时序补偿” 实现同步。

1. 等长布线设计

-

长度偏差控制:不同通道的布线长度差需≤信号周期的 10%,例如 DDR5(频率 3200MHz,周期 0.3125ns),长度差≤31ps 对应的物理长度差≤6mm(信号传播速度≈200mm/ns),实际设计控制在≤5mm;

-

蛇形布线优化:长距离布线需补长时,采用 “小幅度蛇形”(节距 2mm,弧高 0.5mm),避免大幅度蛇形(弧高>1mm)导致的串扰增加(串扰从 - 30dB 降至 - 25dB);

-

分区等长:将大尺寸 PCB 按 “区域划分”(如左、中、右三区),每区内部实现等长,跨区通过中继器补偿时序,例如 0.5m 的 PCIe 4.0 布线,分两区等长,时序差≤30ps。

2. 时序补偿技术

-

延迟匹配:对无法通过布线等长的通道(如绕开连接器的通道),在接收端添加 “延迟线”(如 IDT 的 8T49N240),补偿 50-100ps 的时序差;

-

动态时序调整:在 FPGA 或 CPU 的 IO 口配置 “时序调整单元”(如 Xilinx 的 ISERDES),实时调整采样时钟相位,补偿 ±100ps 的时序偏差。

三、电源分配:满足大电流与低噪声

大尺寸 PCB 常承载多颗高功耗芯片(如服务器 4 颗 CPU,总功耗 600W),需设计 “低阻抗电源分配网络(PDN)”,避免电压跌落(≤5%)与电源噪声(≤50mV)。

1. 大电流布线设计

-

铜箔厚度选择:根据电流计算铜厚,1oz 铜箔(35μm)的电流承载能力:1mm 线宽→1A,2mm→2A,5mm→5A;2oz 铜箔(70μm)可翻倍,例如 20A 的电源回路,2oz 铜箔需线宽 10mm,或采用 “铜皮填充”(面积 20mm×10mm);

-

多路径供电:高电流芯片(如 CPU)采用 “多组电源输入”(如 4 组 12V 输入,每组承载 5A),避免单路径电流过大(>10A)导致的压降;

-

电源平面设计:内层设计 “电源平面”(如 5V、12V 平面),面积≥0.05㎡,平面阻抗≤10mΩ,比布线阻抗(≥100mΩ)低 10 倍,压降减少 90%。

2. 电源噪声抑制

-

去耦电容布局:在每颗芯片的电源引脚旁布置 “高频去耦电容”(0.1μF MLCC),间距≤2mm,每 10mm² 电源平面布置 1 个 “低频去耦电容”(10μF MLCC),电源噪声从 100mV 降至 40mV;

-

电源平面分割:不同电压的电源平面(如 3.3V、5V、12V)需 “隔离分割”,间距≥0.5mm,避免串扰,分割边缘加接地铜箔,噪声减少 15%。

四、接地设计:减少地环流与噪声耦合

大尺寸 PCB 的接地网络若设计不当,会产生 “地环流”(≥100mA)与 “地噪声”(≥20mV),干扰敏感信号(如模拟传感器信号),需通过 “分区接地” 与 “低阻抗接地” 优化。

1. 分区接地设计

-

功能分区:将 PCB 分为 “数字地”(MCU、FPGA)、“模拟地”(传感器、ADC)、“功率地”(电机驱动、电源模块),各区通过 “单点接地” 连接至主接地平面,地环流减少 80%;

-

接地平面优化:内层设计 “完整接地平面”(无开槽、无镂空),接地平面阻抗≤5mΩ,地噪声≤10mV;模拟区域的接地平面需与数字区域隔离,间距≥1mm。

2. 敏感信号接地保护

-

模拟信号接地:模拟传感器信号的接地采用 “星形接地”(所有模拟接地汇总到一个接地点),避免地环流耦合,噪声从 30μV 降至 8μV;

-

屏蔽接地:高速信号的屏蔽层(如同轴电缆、屏蔽布线)需 “单点接地”(仅一端接地),避免形成地环流,辐射干扰减少 25%。

284

284

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?