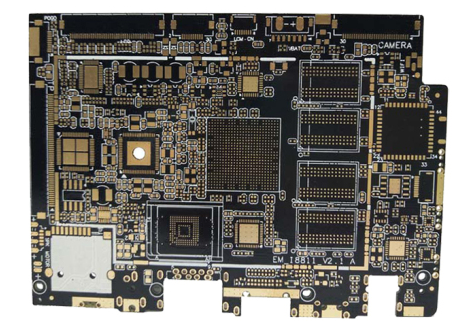

PCB 布局阶段的 “干扰隔离” 是解决 EMC 问题的关键 —— 若布局时未做好隔离,后期布线再优化也难以弥补(如模拟信号被数字噪声耦合,串扰从 - 30dB 降至 - 20dB)。干扰隔离的核心是 “物理分区 + 路径隔离”,通过合理划分 PCB 区域、控制元件间距、规避信号冲突,从源头切断干扰传播路径。今天,我们解析 PCB 布局中最常见的干扰类型、分区隔离方法、冲突规避策略,结合具体参数与案例,帮你实现低干扰布局。

一、PCB 布局中的核心干扰类型与隔离优先级

PCB 中的干扰按 “来源” 可分为三类,隔离优先级从高到低排序:

-

功率 - 信号干扰:功率元件(如电机驱动、DC-DC 转换器)工作时产生大电流波动(1-10A)与强电磁辐射,干扰敏感信号(如模拟采样、高频通信),隔离优先级最高,间距需≥15mm;

-

模拟 - 数字干扰:数字电路(如 MCU、FPGA)的时钟信号(100MHz 以上)产生高频噪声,干扰模拟电路(如运算放大器、传感器),隔离优先级次之,间距需≥10mm;

-

高频 - 低频干扰:高频信号(≥1GHz)的辐射干扰低频信号(≤1MHz),或低频电源噪声耦合至高频电路,隔离优先级第三,间距需≥8mm。

二、信号分区布局:物理隔离的核心方法

信号分区是将 PCB 按 “信号类型” 划分为独立区域,每个区域有明确的功能定位,区域间预留隔离带,避免干扰交叉。

1. 经典分区方案(四层板为例)

-

顶层:数字区(MCU、FPGA、通信接口)+ 高频区(射频模块、高速接口);

-

内层 1:模拟地平面(完整无开槽);

-

内层 2:电源平面(按电压分区:3.3V、5V、12V);

-

底层:模拟区(ADC、传感器、放大器)+ 功率区(DC-DC、功率管);

-

隔离带:各区域间预留≥2mm 的隔离带(无元件、无布线),模拟区与数字区隔离带≥5mm。

2. 分区布局实操要点

-

模拟区布局:

-

敏感元件(如低噪声放大器、高精度 ADC)布局在 PCB 中心,远离板边与干扰源;

-

模拟信号路径最短(≤5mm),避免穿越数字区或功率区;

-

示例:电化学传感器与放大器间距 3mm,放大器与 ADC 间距 4mm,均位于模拟区中心,与数字区隔离带 6mm,采样噪声≤10μV。

-

-

功率区布局:

-

功率元件(DC-DC、功率管)布局在 PCB 边缘,便于散热与接线;

-

功率回路(输入→功率管→输出)路径最短(≤8mm),减少大电流路径的电磁辐射;

-

示例:12V 转 5V DC-DC 转换器布局在 PCB 边缘,输入输出电容紧贴芯片,功率回路长度 6mm,辐射干扰从 45dBμV/m 降至 32dBμV/m。

-

-

数字区布局:

-

数字核心元件(MCU、FPGA)布局在 PCB 中心,外设(如按键、LED)围绕核心元件布局;

-

高频时钟元件(晶振)靠近 MCU,与模拟区间距≥12mm,避免时钟噪声辐射。

-

三、信号路径冲突规避:减少耦合干扰

信号路径冲突是指不同类型信号的布线交叉、平行,导致耦合干扰,布局阶段需提前规划路径,避免冲突。

1. 路径规划原则

-

避免平行布局:干扰源信号与敏感信号的元件摆放避免平行,平行长度≤2mm,交叉时需垂直;例如数字时钟线与模拟采样线垂直交叉,串扰从 - 25dB 降至 - 40dB。

-

缩短耦合路径:干扰源与敏感元件的连线避免长距离靠近,间距≥3 倍线宽(如线宽 0.5mm,间距≥1.5mm)。

-

利用接地隔离:在干扰源与敏感元件之间布置接地铜箔或接地过孔阵列(间距≤2mm),形成 “屏蔽墙”,隔离效果提升 50%。

2. 特殊场景冲突规避

-

高压 - 低压冲突:高压电路(≥220V)与低压电路(≤36V)分区布局,隔离带≥10mm,高压元件布局在 PCB 边缘,远离人手可触及区域;

-

高频 - 射频冲突:WiFi、蓝牙等射频模块布局在 PCB 角落,远离数字时钟、电源模块,射频天线区域无其他元件遮挡,确保信号辐射。

案例:某工业控制 PCB 初期布局时,数字区与模拟区未分区,DC-DC 转换器与 ADC 间距 8mm,导致 ADC 采样误差 3%;优化后按 “数字区 - 隔离带 - 模拟区 - 功率区” 布局,DC-DC 与 ADC 间距 15mm,隔离带 5mm,采样误差降至 0.5%,EMC 辐射测试达标。

286

286

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?