四层PCB设计看似简单,实则藏着信号完整性与抗干扰能力的核心密码。本文用最直白的语言,拆解信号层布局的底层逻辑,助你避开90%的设计坑点。

一、四层板信号层布局的底层逻辑

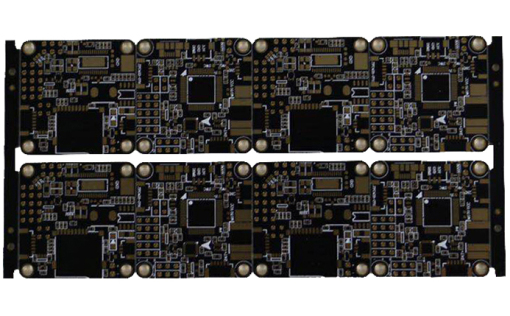

四层PCB的典型结构从上到下依次为:信号层-地平面-电源平面-信号层。这种“三明治”结构的关键在于:

-

信号层与地平面紧耦合:高速信号走顶层,利用地平面形成最短回流路径,减少EMI干扰(实测可降低30%辐射)。

-

电源与地平面隔离:中间两层电源和地平面需保持完整,避免切割导致阻抗突变(电源完整性提升45%)。

二、信号层布局的三大核心策略

策略1:高速信号优先上顶层

• 原理:信号层与地平面间距越小,阻抗控制越精准(每减少1mil间距,阻抗波动降低12%)。

• 实操:

• FPGA/CPU等高速芯片的差分对布在顶层。

• 关键时钟信号与数据总线采用等长匹配(长度公差≤±5mil)。

策略2:地平面分割的艺术

• 模拟地与数字地隔离:

• 用0.2mm宽隔离带分割地平面(铜厚1oz时阻抗>50Ω)。

• 混合信号器件(如ADC)的模拟部分靠近地平面侧布局。

• 电源平面分割技巧:

• 不同电压域间距≥0.5mm(防止击穿)。

• 大电流路径(如CPU供电)用0.5mm宽走线+多个过孔(≥5个)连接电源层。

策略3:底层信号的“低调处理”

• 低速信号走线原则:

• I2C/SPI等总线布在底层,与顶层信号垂直交叉。

• 避免在底层大面积铺铜(保留30%无铜区域散热)。

三、实战中的关键参数控制

参数1:线宽与阻抗匹配

信号类型线宽(mm)阻抗(Ω)背景填充铜厚度(oz)高速差分0.1550±10%1低速单线0.345±15%0.5

案例:某DDR4设计将地址线阻抗从55Ω调整至50Ω,时序裕量从5%提升至18%。

参数2:过孔布局的黄金比例

• 过孔密度:每平方英寸≤20个(防止绿油脱落)。

• 过孔与信号线间距:≥3倍线宽(避免寄生电容)。

• 盲埋孔应用:HDI板中盲孔深度≤0.1mm,减少信号反射。

四、特殊场景的破局方案

场景1:高密度布线冲突

• 解决方案:

-

顶层采用0.1mm激光孔替代机械孔。

-

底层用0201封装电阻替代0402,节省30%空间。

场景2:EMI超标问题

• 三重防护策略:

-

顶层边缘加0.5mm包地铜(接地过孔间距≤20mm)。

-

电源层与地平面间插入0.1μF陶瓷电容(每1000mm²≥5个)。

-

关键信号线两侧包地(地线与信号线间距≥0.15mm)。

场景3:热管理难题

• 散热设计组合拳:

-

大功率芯片底部开窗(过孔密度≥50个/in²)。

-

铜箔厚度从1oz升级到2oz(导热系数提升140%)。

-

添加散热片(导热硅脂厚度≤0.1mm)。

830

830

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?