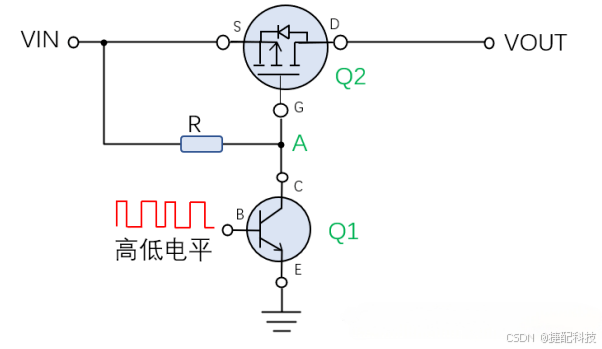

此电路包含 Q1(NPN 三极管)与 Q2(PMOS 管),由 MCU 凭借高低电平掌控三极管 Q1 的导通与关断状态。当 Q1 处于关断时,因电阻 R 无电流通过,A 点电位等同于 Vin,即 Q2 的栅极电压 VG 为 Vin,同时其源极电压 VS 也为 Vin,如此一来 Q2 的 G、S 两端电压差为 0,致使 Q2 关断,此时 VOUT 无输出。而当 Q1 导通,A 点电压降为 0,Q2 的 G、S 电压变为 0 - Vin = -Vin,一旦 -Vin 达到 Q2 的导通门限电压,Q2 便导通,VOUT 得以输出。

开关管 Q1 可在 NMOS 与 NPN 三极管之间抉择,其选择依据 MCU 的 IO 电压,要确保所选 MOS 管的开启电压高于三极管的开启电压。限流电阻 R2 的取值取决于 MCU 的 IO 电压、最大输出电流以及开关管 Q1 的类型。一般而言,MOS 管的限流电阻取值在几十 Ω 范围,三极管的限流电阻则需依据 MCU 的 IO 电压与最大输出电流计算,通常处于 kΩ 级别。

上下电阻 R3 兼具上拉与下拉电阻的功能,具体取决于 VOUT 的默认状态。在上电瞬间,MCU 尚未就绪,此时需借助电阻来固定电平。若 VOUT 上电默认开启,则 R3 用作上拉电阻,反之则为下拉电阻,上拉电压 VCC 即为 MCU 的 IO 供电电压。

在 PMOS 的 GS 之间并联电容 C,当开启 PMOS 时,先对电容 C 充电,使 PMOS 的 VGS 从 0 逐步上升,让 PMOS 经可变电阻进入饱和区,以此避免在开通瞬间因后级电路诸多因素致使 PMOS 遭受大电流冲击。GS 电阻 R1 的取值多在几十上百 KΩ,这有助于降低 Q1 导通时的功耗。不过需留意,R1 为 MOS 的 GS 电容构建了放电回路,若 R1 取值过大,会造成 MOS 管关断速度减缓。

827

827

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?