文章目录

结论:组合逻辑‘;req[0] > req[1] > …;req与其补码进行相与,得到的独热码即是grant!

一、题目

数字IC工程师在使用多主设备的总线过程中,需要考虑到不同主设备申请总线控制权的优先级问题,请使用Verilog语言,考虑四个主设备,设计固定优先级仲裁器,该仲裁器默认时的总线控制的优先级永远保持为为A>B>C>D。

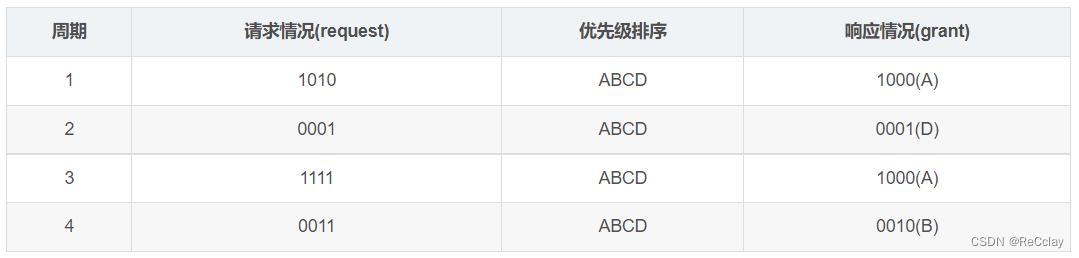

默认情况下的优先级排序为A>B>C>D,input 请求情况request 的四位二进制,从高到低也分别代表主设备A、B、C、D的总线控制请求,output的grant输出one hot编码,即“1000,0100,0010,0001”四种情况中的一种,给出的案例如下,按照四个周期依次输入控制请求,仲裁器在按照固定优先级算法的条件下会依次响应设备A,D,A,B

注:虽然我们在上面的例子中提出周期的概念,但对于仲裁器来讲,它是一个纯组合逻辑电路。

本文介绍了数字IC工程师如何使用Verilog设计固定优先级仲裁器,针对四个主设备A>B>C>D设定优先级。文章详细讲解了通过case/if语法、for循环和补码相与法三种方法实现仲裁器,并提供了理论知识和代码实现。

本文介绍了数字IC工程师如何使用Verilog设计固定优先级仲裁器,针对四个主设备A>B>C>D设定优先级。文章详细讲解了通过case/if语法、for循环和补码相与法三种方法实现仲裁器,并提供了理论知识和代码实现。

订阅专栏 解锁全文

订阅专栏 解锁全文

2404

2404

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?