有限状态机实现仲裁器

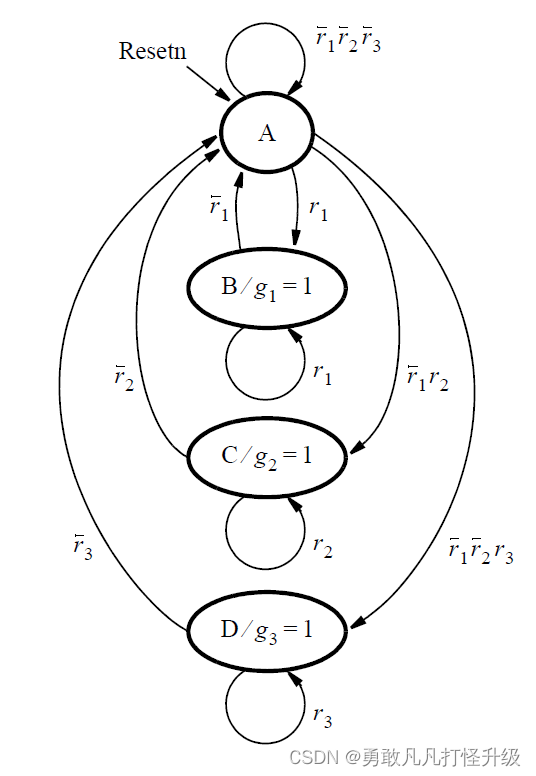

状态图如下:

题目要求:

这个FSM作为一个仲裁器电路,控制着三个请求设备对某种类型资源的访问。每个设备通过设置一个信号r[i]=1来提出对资源的请求,其中r[i]是r[1]、r[2]或r[3]。每个r[i]是FSM的一个输入信号,代表三个设备中的一个。只要没有请求,FSM就会保持在状态A。当一个或多个请求发生时,FSM决定哪个设备收到使用资源的授权,并改变到一个状态,将该设备的g[i]信号设置为1。每个g[i]是FSM的一个输出。有一个优先级系统,即设备1比设备2的优先级高,设备3的优先级最低。因此,举例来说,当FSM处于状态A时,设备3只有在它是唯一提出请求的设备时才会收到授予。一旦设备i被FSM授予授予,只要它的请求r[i]=1,该设备就会继续收到授予。

编写完整的Verilog代码来表示这个FSM。

module top_module (

input clk,

input resetn, // active-low synchronous reset

input [3:1] r, // request

output [3:1] g // grant

);

reg [2:0]state,next_state ;

parameter A=3'b000,B=3'b001,C=3'b010,D=3'b100;

//FF

always@(posedge clk)begin

if(!resetn)

state<=A;

else

state<=next_state;

end

//Transition

always @(*) begin

case (state)

A:

casez(r) //优先级判断,也可以用if-else

3'b000:next_state=A;

3'bzz1:next_state=B;

3'bz1z:next_state=C;

3'b1zz:next_state=D;

default:next_state=A;

endcase

B: //被授权后只用考虑r1变化

next_state=r[1]?B:A;

C:

next_state=r[2]?C:A;

D:

next_state=r[3]?D:A;

default:

next_state=A;

endcase

end

//output

always@(*)begin

g=3'b000; //default_state

case(state)

B:

g[1]=1'b1;

C:

g[2]=1'b1;

D:

g[3]=1'b1;

endcase

end

endmodule

if-else判断A状态的优先级:

A:

if(r == 3'b000)

next_state = A;

else if(r[1])

next_state = B;

else if(r[2:1] == 2'b10)

next_state = C;

else if(r == 3'b100)

next_state = D;

else

next_state=A;

2430

2430

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?