2.9 逻辑函数形式的变换

在前面所讲的逻辑函数化简方法中,都是以最简与或式作为化简目标的。然而在用电路实现这些逻辑函数时,这种最简与或式有时并不是理想的形式。这是因为在电路实现的过程中,往往可供选择的电子器件种类有限,所以必须把逻辑函数的形式变换为与所用器件相适应的形式。

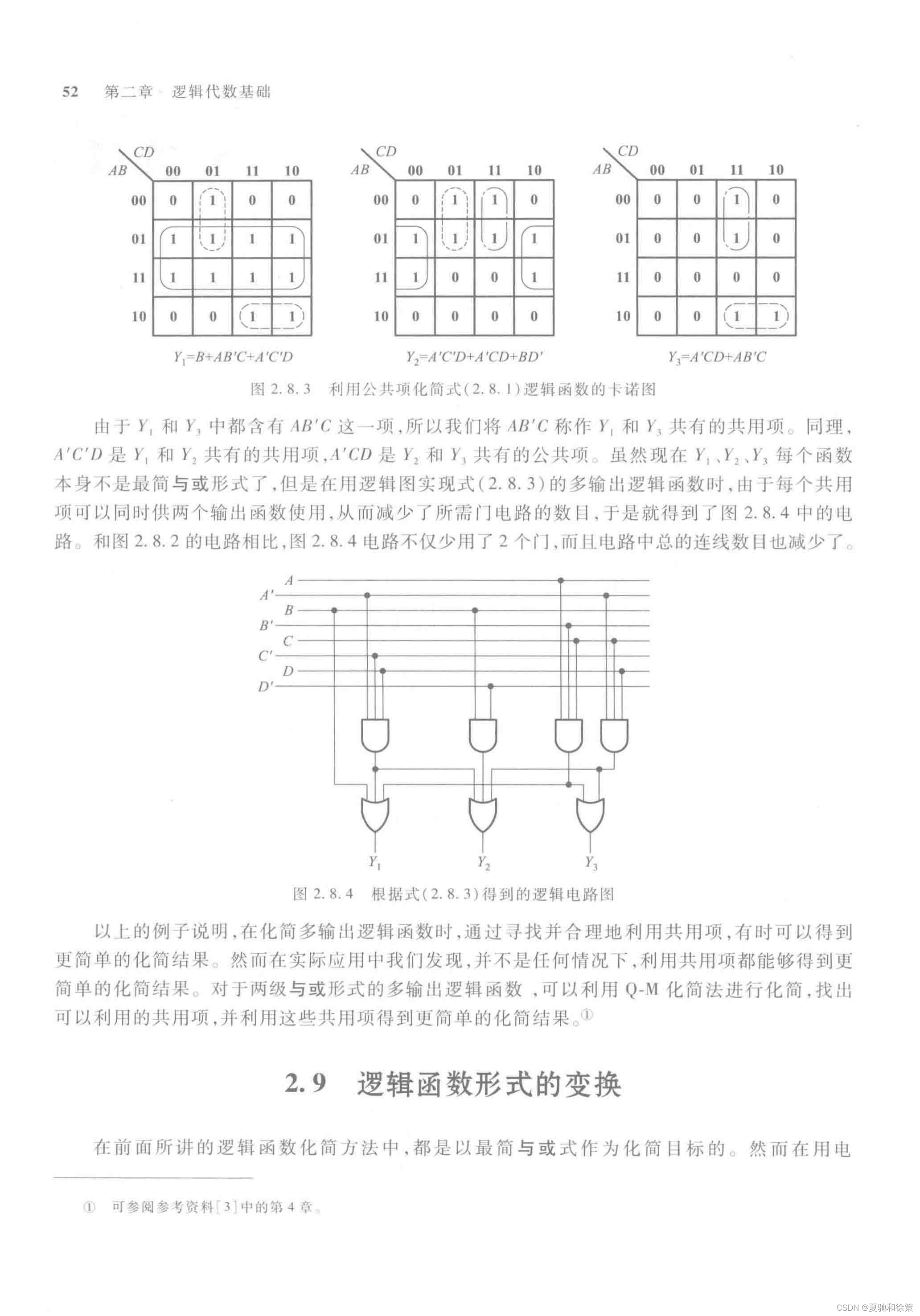

2.9.1 逻辑函数形式变换的必要性

在使用标准化的数字集成电路组成所需的逻辑电路时,不仅受到所提供的门电路类型的限制,而且由于很难找到具有4个以上输入端的与门和或门,因而当与或逻辑函数式的输入变量数和乘积项数很大时,就无法用一个两级的与或电路实现这个逻辑函数。

在 PLD(可编程逻辑器件)中,虽然某些 PAL 型 PLD 可以满足生成多输入变量、多乘积项的与或逻辑函数的需要,但是在用来实现输入变量数和乘积项数较少的与或逻辑函数时,器件内部的资源将得不到充分利用。因此,在 FPGA 型 PLD 的结构中,所提供的门电路都是输入端不多、逻辑功能种类有限的几种。

例如我们需要用门电路实现式 (2.9.1) 的逻辑函数:

𝑌=𝐴𝐵′𝐶′+𝐴′𝐵𝐶Y=AB′C′+A′BC (2.9.1)

如果有 3 输入端的与门和 2 输入端的或门可以选用,则可以很方便地与上式对应地接成图 2.9.1 的两级与或逻辑电路。

但如果限定只能使用 2 输入端的与非门,这时就需要将式 (2.9.1) 变换为全部由两变量与非运算组成的形式。为此,可利用摩根定理将式 (2.9.1) 进行两次求反运算,变换成与非-与非形式,得到:

𝑌=𝐴𝐵′𝐶′+𝐴′𝐵𝐶=((𝐴𝐵′𝐶′+𝐴′𝐵𝐶)′)′=(((𝐴𝐵′)′𝐶′)′+((𝐴′𝐵)′𝐶)′)Y=AB′C′+A′BC=((AB′C′+A′BC)′)′=(((AB′)′C′)′+((A′B)′C)′) (2.9.2)

按照上式就得到了全部由 2 输入端与非门组成的逻辑电路,如图 2.9.2 所示。其中 G1 和 G2 两个与非门被接成了反相器使用。

如果有异或门和与门可以使用,则应当将式 (2.9.1) 变换成下面的形式:

𝑌=𝐴𝐵′𝐶′+𝐴′𝐵𝐶=(𝐴⊕𝐵)𝐶Y=AB′C′+A′BC=(A⊕B)C (2.9.3)

根据上式就得到了图 2.9.3 的逻辑电路。

2.9.2 实例分析

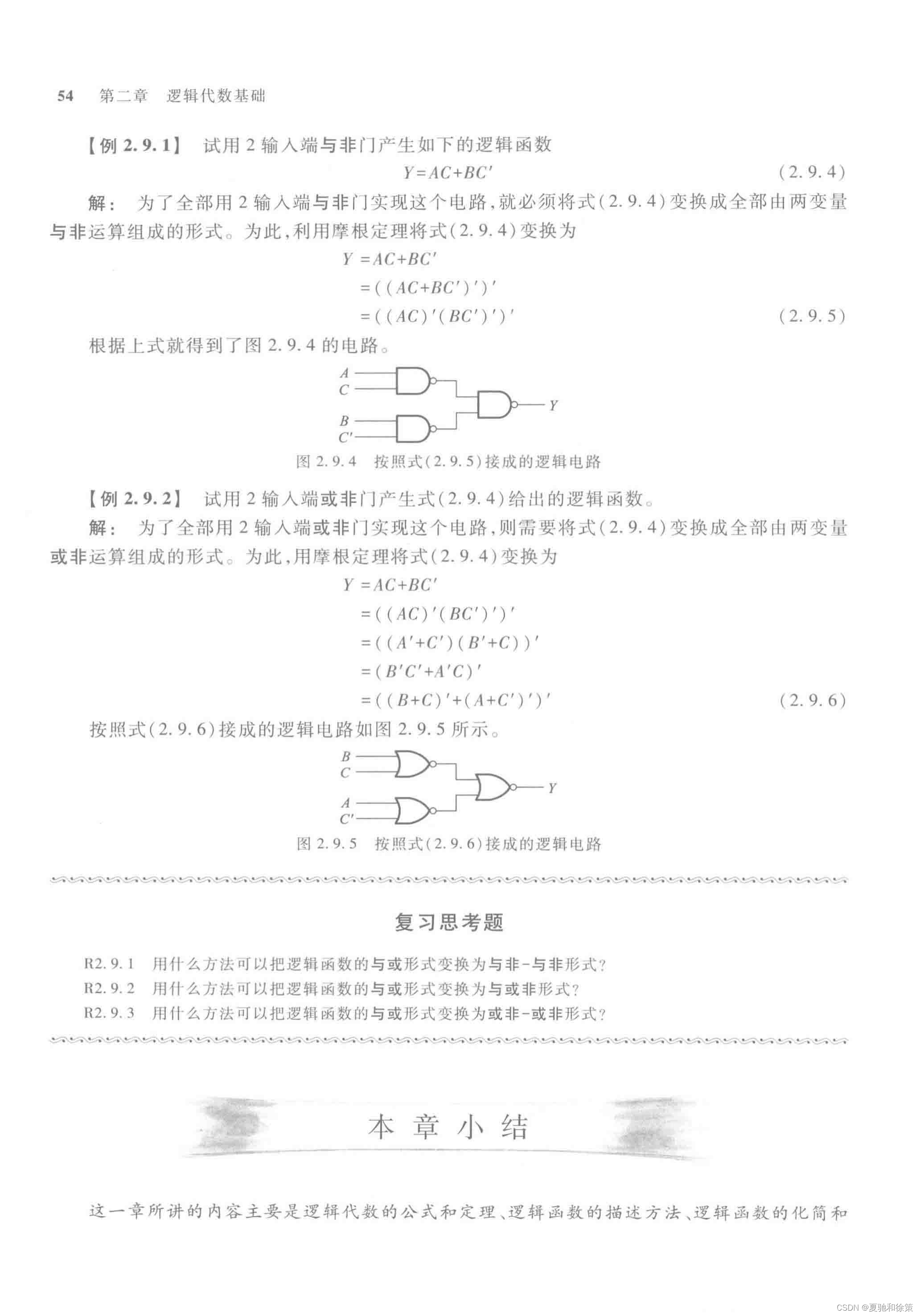

例 2.9.1 试用 2 输入端与非门产生如下的逻辑函数:

𝑌=𝐴𝐶+𝐵𝐶′Y=AC+BC′ (2.9.4)

解:为了全部用 2 输入端与非门实现这个电路,就必须将式 (2.9.4) 变换成全部由两变量与非运算组成的形式。为此,利用摩根定理将式 (2.9.4) 变换为:

𝑌=𝐴𝐶+𝐵𝐶′=((𝐴𝐶)′(𝐵𝐶′)′)′Y=AC+BC′=((AC)′(BC′)′)′ (2.9.5)

根据上式就得到了图 2.9.4 的电路。

例 2.9.2 试用 2 输入端或非门产生式 (2.9.4) 给出的逻辑函数。

解:为了全部用 2 输入端或非门实现这个电路,则需要将式 (2.9.4) 变换成全部由两变量或非运算组成的形式。为此,用摩根定理将式 (2.9.4) 变换为:

𝑌=𝐴𝐶+𝐵𝐶′=((𝐴′+𝐶′)(𝐵′+𝐶))′Y=AC+BC′=((A′+C′)(B′+C))′ (2.9.6)

按照式 (2.9.6) 接成的逻辑电路如图 2.9.5 所示。

本章小结

这一章所讲的内容主要是逻辑函数的公式和定理、逻辑函数的描述方法、逻辑函数的化简和变换这三部分。

为了进行逻辑运算,必须熟练掌握表 2.3.1 中的基本公式。至于表 2.3.3 中的常用公式,完全可以由基本公式导出。尽管如此,掌握尽可能多的常用公式仍然是十分有益的,因为直接引用这些公式可以大大提高运算效率。

在逻辑函数的描述方法中,共介绍了五种描述方法,即真值表、逻辑函数式、逻辑图、波形图和卡诺图。这几种方法之间可以任意地互相转换。根据具体的使用情况,可以选择最适当的一种方法描述所研究的逻辑函数。

在逻辑函数化简方法当中,一共介绍了三种方法——公式化简法、卡诺图化简法和 Q-M 法。公式化简法的优点是它的使用不受任何条件的限制。但由于这种方法没有固定的步骤可循,所以在化简复杂的逻辑函数时,不仅需要熟练地使用各种公式和定理,而且需要有一定的运算技巧和经验。

卡诺图化简法是一种通过合并最小项进行化简的方法。它的优点是简单、直观,而且有一定的化简步骤可循。初学者容易掌握这种方法,而且化简过程中也易于避免出差错。然而在逻辑变量超过 5 个以上时,将失去简单、直观的优点,因此也就没有多大的实用价值了。

Q-M 法的基本原理仍然是通过合并最小项的方法来化简逻辑函数。但由于 Q-M 法有一定的化简步骤,所以适合于机器运算。这种方法已经被用于编制分析和设计数字电路的计算机程序。

在具体设计数字电路的过程中,通常可供使用的器件类型是有限的,这就需要利用逻辑函数的公式和定理,将函数式化成与所用器件逻辑类型相适应的形式,而不一定是最简的与或形式。变换后的逻辑函数式可能既不是由单一的与非运算组成的,也不是由单一的或非运算组成的,而且可能是多级函数式。因此,究竟将函数式化成什么形式最有利,要根据选用哪些类型的电子器件而定。此外,在化简一组多输出逻辑函数时,不应仅以孤立地求出每个函数输出的最简形式为目标,而应通过找出并合理利用共用项,以求得总体最简的化简结果。

鉴于现代的数字电路规模日益庞大,产品更新的周期越来越短。因此,使用已有的电路模块组成所需要的逻辑电路已经成为设计人员经常使用的方法。这种方法不仅可以提高设计速度,而且有利于降低设计成本。在后面的章节里还将看到,采用模块电路进行设计时,同样需要将逻辑函数式变换成与所用模块电路相适应的形式。

目前用于数字集成电路设计和 PLD 开发的 EDA 软件中,一般都具备逻辑函数化简和变换的功能。在使用这些 EDA 软件进行设计时,逻辑函数的化简和变换工作都是由计算机完成的。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?