5.6 硬布线控制器和门阵列控制器

一、硬布线控制器

硬布线控制器,也被称为组合逻辑控制器,是早期计算机设计中采用的一种方法。该控制器将控制部件视为一个专门生成固定时序控制信号的逻辑电路。这种逻辑电路的设计目标是使用最少的元件实现最高的操作速度。一旦这种控制部件被构建完成,除非进行重新设计和物理布线,否则无法添加新的控制功能。硬布线控制器由门电路和触发器组成一个复杂的树形网络,因此得名。

硬布线控制器是计算机中最复杂的逻辑部件之一。当执行不同的机器指令时,它通过激活一系列相互不同的控制信号来解释指令,结果通常是控制器结构不明确且混乱。这种结构上的缺陷使得硬布线控制器的设计和调试非常复杂且成本高昂。因此,随着微程序控制器的出现,硬布线控制器逐渐被替代。然而,随着第四代计算机和VLSI技术的发展,随机逻辑设计思想再次受到重视。

图5.35展示了硬布线控制器的结构框图。其逻辑网络的输入信号来源有三个:1)来自指令操作码译码器的输出1;2)来自执行部件的反馈信息B;3)来自时序生成器的时序信号,包括机器周期信号M和时钟周期信号T。硬布线控制器的基本原理是:微操作控制信号C是指令操作码译码器输出、时序信号和状态条件信号的函数,即C=f(I, M, T, B)。这些控制信号是通过门电路、触发器等多种器件采用组合逻辑设计方法实现的。当机器加电工作时,某一操作控制信号C会在特定指令和状态条件下激活。

二、门阵列控制器

门阵列控制器是一种更为灵活的设计,利用预先设计的芯片阵列,通过编程实现不同的逻辑功能。与硬布线控制器相比,门阵列控制器可以在不改动硬件的情况下,通过重新编程来适应新的控制需求。这种控制器通常采用可编程逻辑设备(如PLD、FPGA)来实现控制逻辑,使其更容易适应不断变化的技术需求和功能升级。

门阵列控制器的主要优势在于它的可编程性,允许在产品完成后快速修改和调整其功能,大大减少了重新设计和生产的成本和时间。此外,通过使用现代的设计工具,门阵列控制器可以实现更复杂的控制逻辑,提供更高的性能和更好的资源优化。

在现代计算机系统和复杂电子设备中,门阵列控制器提供了一种高效、灵活的解决方案,适用于各种高速、高复杂性的控制任务。随着电子技术的不断进步,门阵列控制器的应用范围也在持续扩展,成为现代电子设计中不可或缺的一部分。

二、通用可编程逻辑器件

通用可编程逻辑器件(Generic Programmable Logic Devices, GPLD)是现代电子设计中不可或缺的元素,尤其在需要灵活性和可扩展性的场合。从1970年代开始,随着大规模集成电路制造技术的进步,这些设备逐渐成为设计者的首选。

1. 74系列标准逻辑器件

74系列标准的小规模/中规模逻辑器件广泛应用于各种电子系统中。它们通常只包含一种逻辑功能,因此设计组合逻辑时往往需要使用多个不同种类的芯片。这种设计方法的优点包括高速和优化的电路结构,但同时也存在一些缺点,如使用器件数量多、功耗大、电路板布线复杂、体积大、可靠性较低、成本高且不易修改和调试。

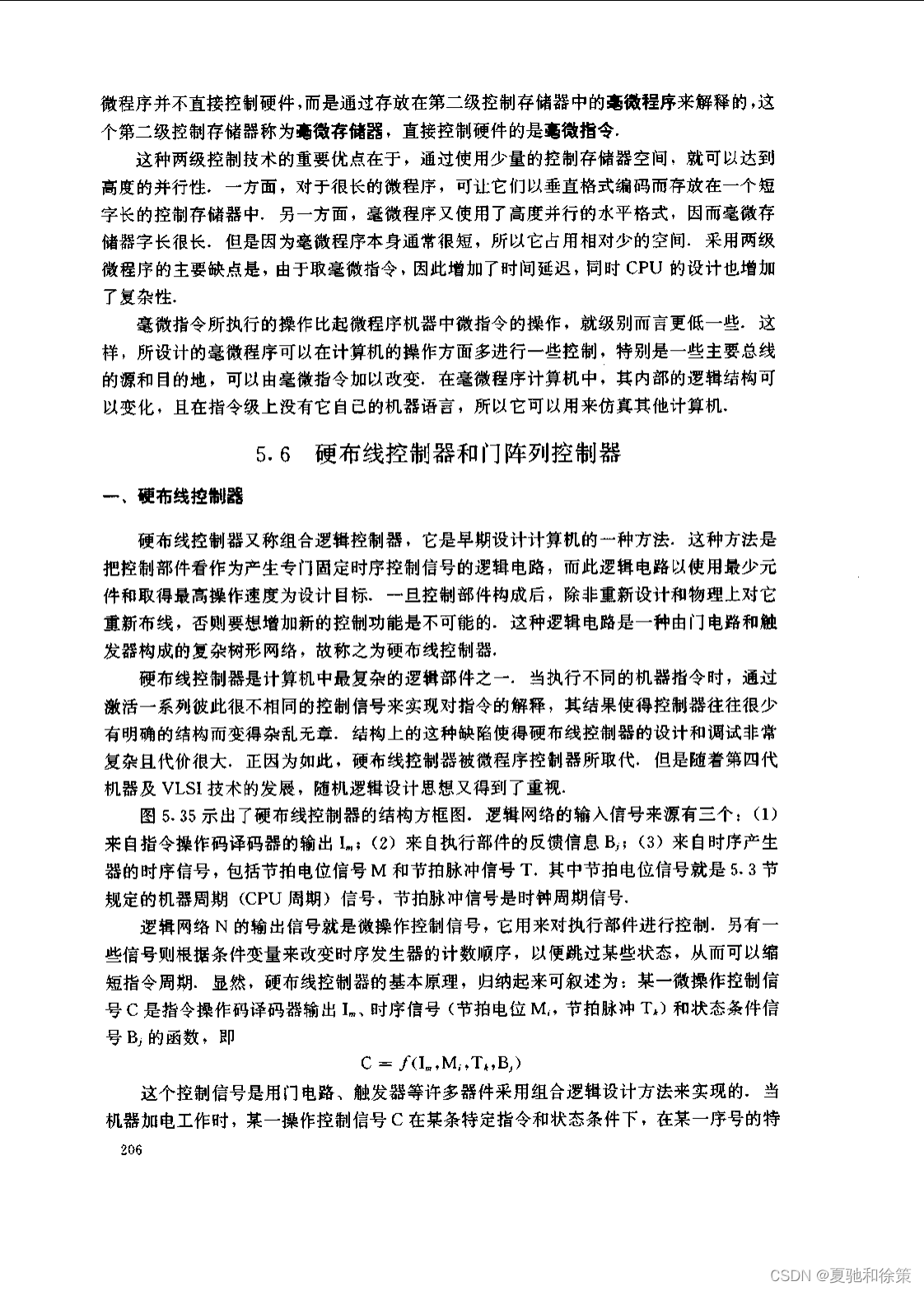

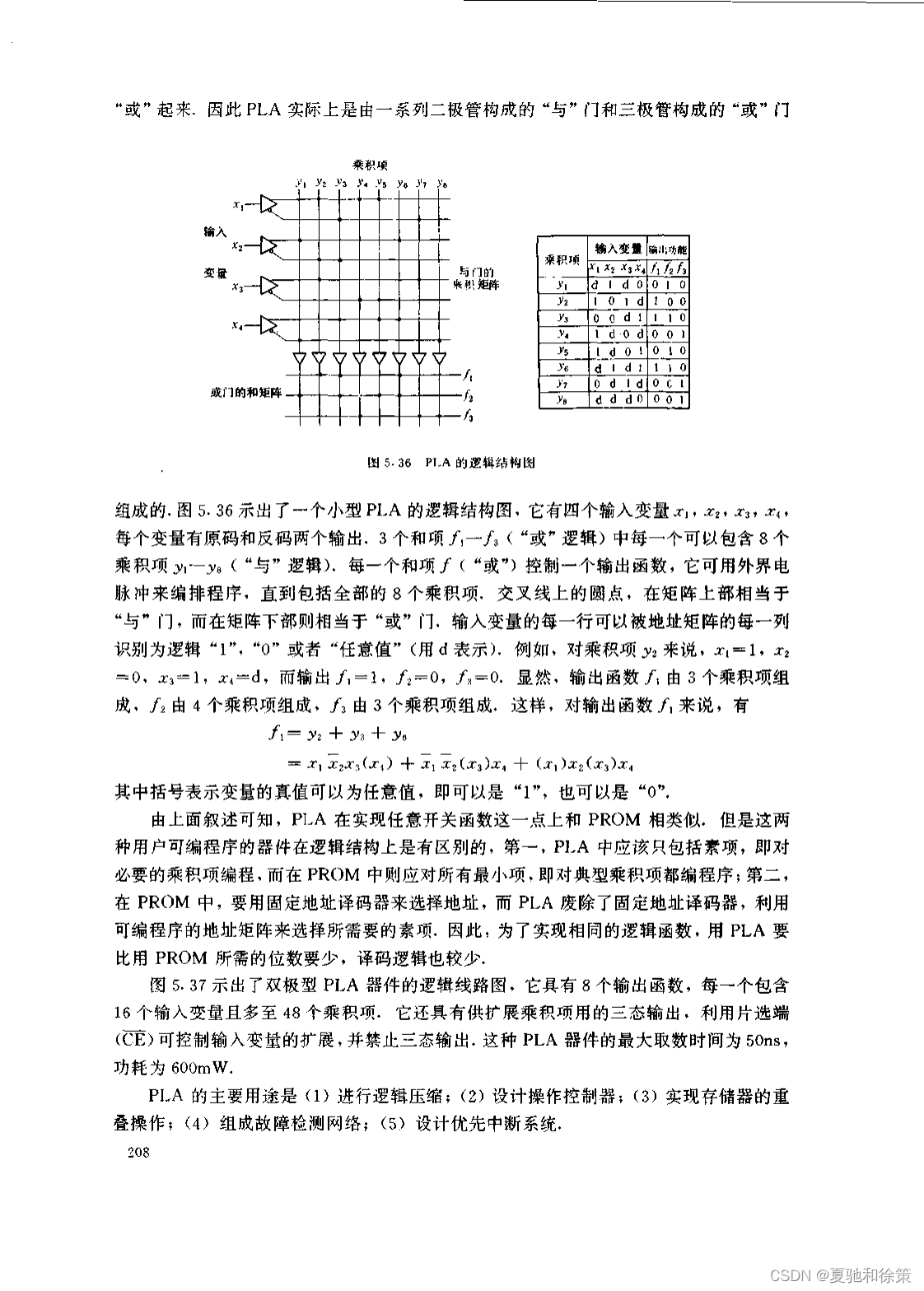

2. 可编程逻辑阵列(PLA)

PLA 设备通过一系列的“与”门和“或”门实现逻辑功能,这些门通过二极管和三极管组成,并可以在任意输出端进行“或”操作。PLA是一次性编程器件,利用熔丝技术确定逻辑连接。PLA的主要用途包括逻辑压缩、设计操作控制器、存储器重叠操作、故障检测网络和设计优先中断系统。

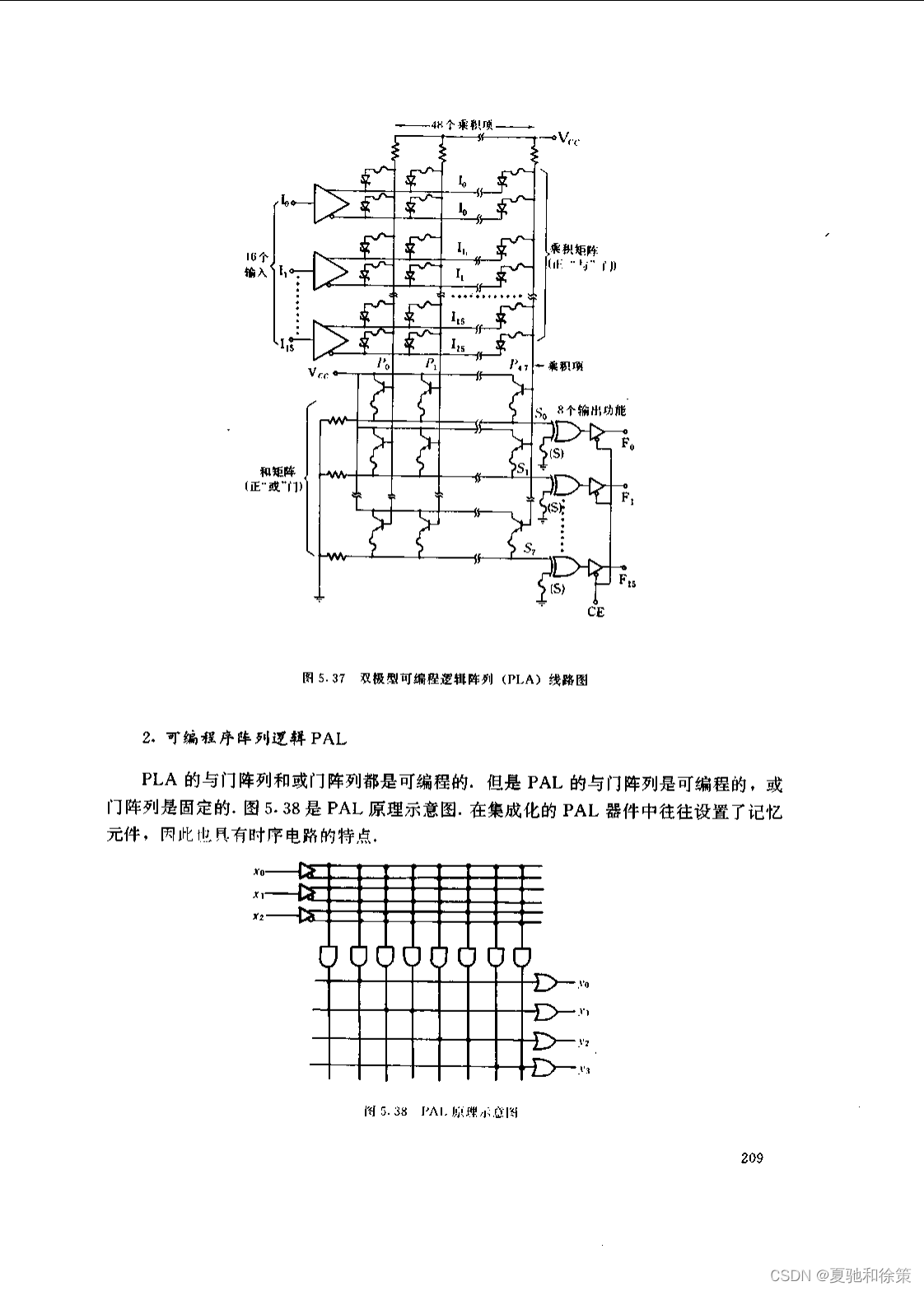

3. 可编程阵列逻辑(PAL)

与PLA不同,PAL的“与”门阵列是可编程的,而“或”门阵列是固定的。这种设计允许PAL在集成化设备中具有时序电路的特性。PAL的每种芯片功能有一定的限制,因此设计时需要根据功能需求选择合适的型号。

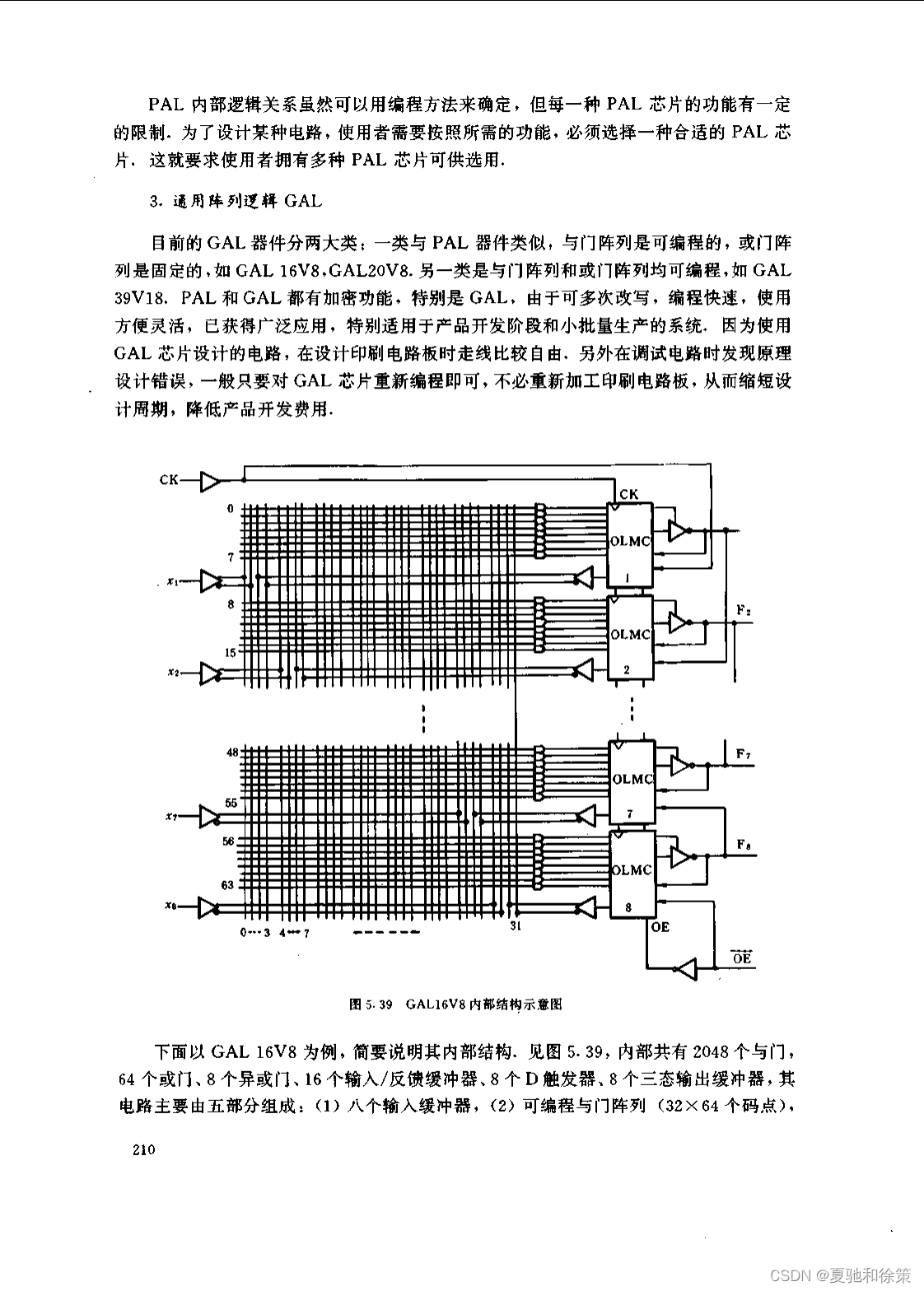

4. 通用阵列逻辑(GAL)

GAL是对PAL技术的改进,使用E²CMOS工艺,不仅可以多次编程,而且具有更快的编程速度和更高的灵活性。GAL器件在设计和调试电路时特别方便,因为即便发现设计错误也只需重新编程GAL芯片,而无需重新制作电路板,这大大缩短了设计周期和降低了成本。GAL的结构允许它替代所有现有的PAL器件,并可配置为组合逻辑或时序逻辑,输出宏单元也可根据需要设置为高或低有效。

结论

通用可编程逻辑器件代表了现代电子设计中一种趋势,即向更高的灵活性和可扩展性转变。这些器件的应用从简单的逻辑操作扩展到复杂的系统控制和逻辑优化,是现代电子设计工程师的重要工具。随着技术的不断发展,我们可以预见这些器件将在未来的电子产品和系统中扮演更加关键的角色。

三、门阵列控制器

1. 基本思想

当使用门阵列器件设计控制器时,其基本设计思想源自早期的硬布线控制器:先定义每个操作控制信号的逻辑表达式,再选用适合的门阵列芯片,并通过编程实现这些表达式。例如,在使用可编程逻辑阵列(PLA)设计微操作控制信号时,指令的操作码、节拍电位、节拍脉冲和反馈状态条件作为输入,通过编排的“与-或”逻辑阵列产生所需的微操作控制信号,如:

C=f(I,M,T,B)

其中,C 是微操作控制信号,I 是操作码,M 是节拍电位,T 是节拍脉冲,B 是反馈条件。这表明,虽然门阵列控制器是组合逻辑控制器,但与早期的硬布线控制器不同的是,它通过程序可编的方式,不需通过硬联线连接实现。

2. 指令执行流程

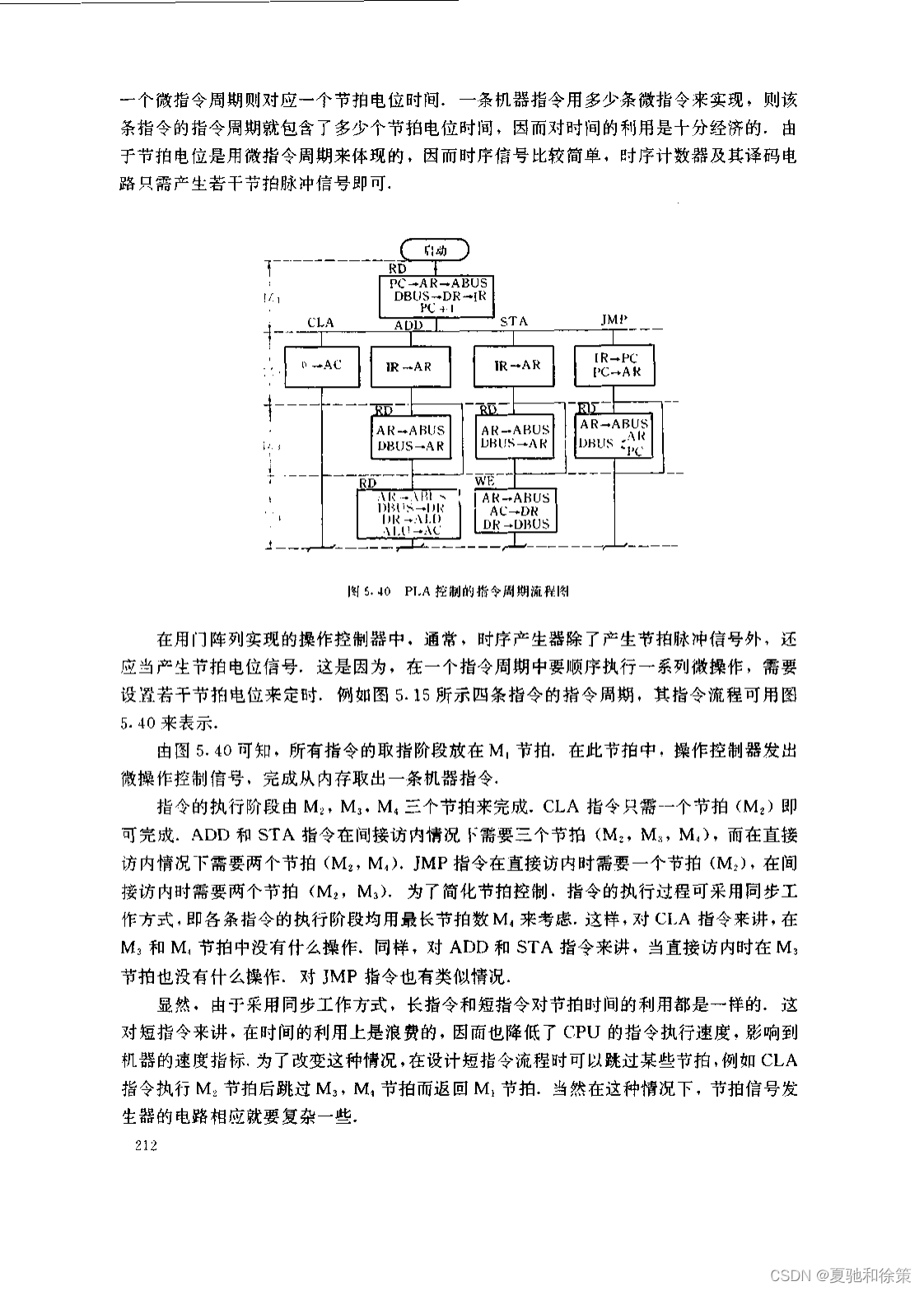

在微程序控制器中,一个机器指令周期对应一个微程序,而每个微指令周期则对应一个节拍电位时间。例如,指令的执行阶段可能需要多个节拍电位来完成。PLA控制的指令周期流程如下:

- 取指阶段:所有指令的取指阶段放在M1节拍中,在此节拍中操作控制器发出微操作控制信号以从内存取出机器指令。

- 执行阶段:如图所示,不同的指令如CLA、ADD、STA和JMP在M2到M4的节拍中完成。例如,CLA指令只需一个节拍(M2)即可完成,而ADD和STA指令在间接访问内存情况下需要三个节拍(M2, M3, M4),直接访问内存时需要两个节拍(M2, M4)。JMP指令在直接访问内存时需要一个节拍(M2),间接访问时需要两个节拍(M2, M3)。

通过这种设计,短指令和长指令对节拍时间的利用都是一样的,这虽然简化了节拍控制,但也可能造成对短指令节拍时间的浪费,从而降低CPU的指令执行速度。

3. 微操作控制信号的产生

在门阵列控制器中,微操作控制信号的产生与微程序控制器不同。在微程序控制器中,微操作控制信号由微指令产生,可以重复使用。而在门阵列控制器中,微操作控制信号由门阵列器件的某一输出函数产生。

设计这些控制信号的过程包括根据所有机器指令流程图寻找出产生同一个微操作信号的所有条件,并与适当的节拍电位和节拍脉冲组合,然后编写其逻辑表达式并在门阵列器件中进行编程。设计时需特别注意控制信号是电位有效还是脉冲有效,若是脉冲有效,则必须加入节拍脉冲信号进行“与”操作。

这种门阵列控制器的设计思想体现了组合逻辑技术和存储逻辑技术的结合,为现代电子设备提供了高效灵活的控制方案。

763

763

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?