本小节为大家介绍一种较为常用的存储类 IP 核——ROM 的使用方法。 ROM 是只读存储器(Read-Only Memory)的简称,是一种只能读出事先所存数据的固态半导体存储器。其特性是一旦储存资料就无法再将之改变或删除,且资料不会因为电源关闭而消失。

而事实上在 FPGA 中通过 IP 核生成的 ROM 或 RAM(RAM 将在下一节为大家讲解)调用的都是 FPGA 内部的 RAM 资源,掉电内容都会丢失(这也很容易解释, FPGA 芯片内部本来就没有掉电非易失存储器单元)。用 IP 核生成的 ROM 模块只是提前添加了数据文件(.mif 或.hex 格式),在 FPGA 运行时通过数据文件给 ROM 模块初始化,才使得 ROM 模块像个“真正”的掉电非易失存储器;也正是这个原因, ROM 模块的内容必须提前在数据文件中写死,无法在电路中修改。

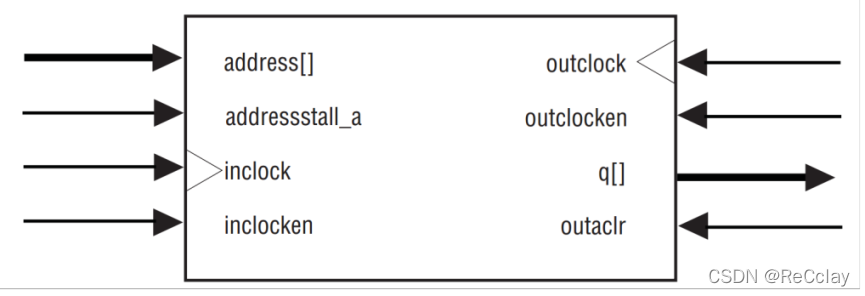

Altera 推出的 ROM IP 核分为两种类型:单端口 ROM 和双端口 ROM。对于单端口ROM 提供一个读地址端口和一个读数据端口,只能进行读操作;双端口 ROM 与单端口ROM 类似,区别是其提供两个读地址端口和两个读数据端口,基本上可以看做两个单口RAM 拼接而成。下面给出 ROM 不同配置模式存储器的接口信号图。

本文介绍了FPGA中的ROM IP核,包括只读存储器的特性,以及Altera提供的单端口和双端口ROM类型。ROM内容通过数据文件初始化,无法在电路中修改。并提到在配置ROM IP核后,可以通过生成的例化模块了解所需控制的信号。

本文介绍了FPGA中的ROM IP核,包括只读存储器的特性,以及Altera提供的单端口和双端口ROM类型。ROM内容通过数据文件初始化,无法在电路中修改。并提到在配置ROM IP核后,可以通过生成的例化模块了解所需控制的信号。

订阅专栏 解锁全文

订阅专栏 解锁全文

2155

2155

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?