杂散电容,顾名思义,指的是电路中非预期的、非功能性的电容。这些电容通常存在于电路的各个部分之间。

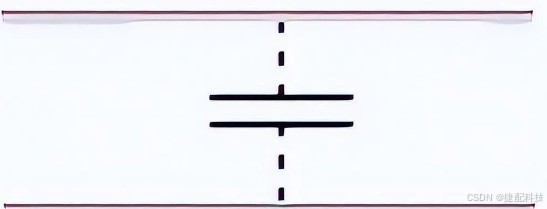

在电路设计中,任何两个不同电位的导体,只要它们足够接近,就会产生电场,从而形成电容。这种电容并非设计者有意为之,而是在电路制造过程中自然形成的,因此被称为杂散电容。

杂散电容可能会干扰电路的正常工作,尤其是在高频应用中,它们可能会引起信号失真或干扰。

二、PCB杂散电容的计算方法

在普通的计算中,杂散电容大小公式:C = Q/V,是对在差分电位上积累的电荷的测量。

在 PCB 设计中,杂散电容大小公式变为 : C= ϵA/D,这意味着电容值与绝缘体的介电常数、面积、导体之间的距离之间的关系。

三、影响PCB杂散电容的因素

杂散电容的产生受到多个因素的影响,主要包括:

- 导体间距:间距越大,杂散电容越小;间距越小,杂散电容越大。

- 导体面积:面积越大,杂散电容越大;面积越小,杂散电容越小。

- 介电材料:介电常数越高的材料,产生的杂散电容越大;介电常数越低的材料,产生的杂散电容越小。

四、降低PCB杂散电容的策略

在高频电路设计中,杂散电容的影响尤为显著,因此需要采取一些措施来减少其影响:

- 优化元件布局:尽量缩短元件引线,并合理分组元件,以减少电容耦合。

- 增加间距:增加元件、组件、走线之间的间距,以降低杂散电容。

- 使用屏蔽技术:在敏感信号线之间添加屏蔽层,以减少电容耦合。

- 调整走线宽度:对于高频信号,适当减小走线宽度可以减少杂散电容。

- 避免大面积平行布线:减少内层地平面的使用,避免导线过度平行布置,以降低杂散电容。

131

131

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?