题目

描述

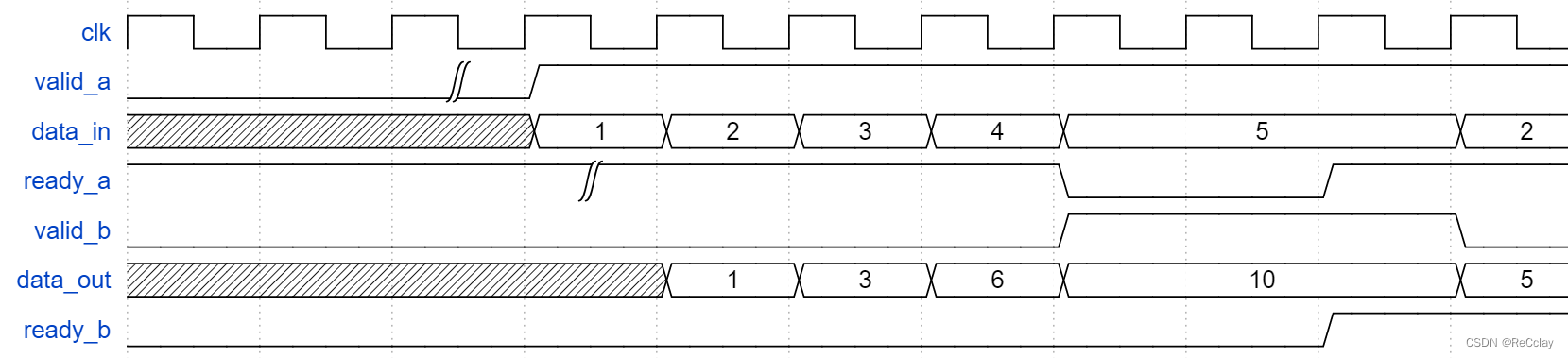

实现串行输入数据累加输出,输入端输入8bit数据,每当模块接收到4个输入数据后,输出端输出4个接收到数据的累加结果。输入端和输出端与上下游的交互采用valid-ready双向握手机制。要求上下游均能满速传输时,数据传输无气泡,不能由于本模块的设计原因产生额外的性能损失。

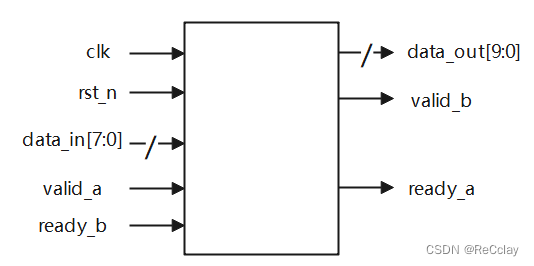

电路的接口如下图所示。valid_a用来指示数据输入data_in的有效性,valid_b用来指示数据输出data_out的有效性;ready_a用来指示本模块是否准备好接收上游数据,ready_b表示下游是否准备好接收本模块的输出数据;clk是时钟信号;rst_n是异步复位信号。

接口时序示意图

输入描述:

input clk ,

input rst_n

该博客详细介绍了如何使用Verilog实现FPGA中8bit数据的串行输入累加及无气泡传输。在接收到4个数据后,模块输出累加结果,遵循valid-ready握手协议。内容包括接口描述、时序分析和解决方案,强调了在数据传输过程中避免性能损失的关键设计点。

该博客详细介绍了如何使用Verilog实现FPGA中8bit数据的串行输入累加及无气泡传输。在接收到4个数据后,模块输出累加结果,遵循valid-ready握手协议。内容包括接口描述、时序分析和解决方案,强调了在数据传输过程中避免性能损失的关键设计点。

订阅专栏 解锁全文

订阅专栏 解锁全文

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?