题目

描述

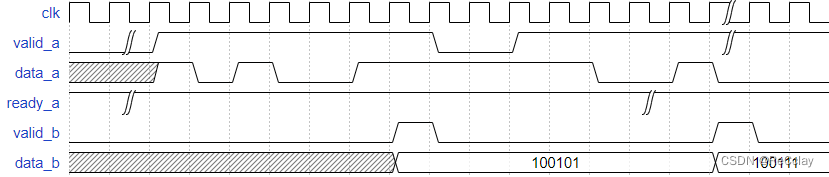

实现串并转换电路,输入端输入单bit数据,每当本模块接收到6个输入数据后,输出端输出拼接后的6bit数据。本模块输入端与上游的采用valid-ready双向握手机制,输出端与下游采用valid-only握手机制。数据拼接时先接收到的数据放到data_b的低位。

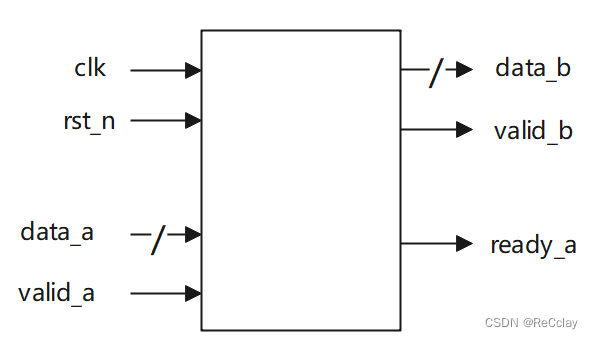

电路的接口如下图所示。valid_a用来指示数据输入data_a的有效性,valid_b用来指示数据输出data_b的有效性;ready_a用来指示本模块是否准备好接收上游数据,本模块中一直拉高;clk是时钟信号;rst_n是异步复位信号。

接口时序示意图

输入描述:

input clk ,

input rst_n ,

input valid_a ,

input data_a

输出描述:

output reg ready_a ,

output reg valid_b ,

output reg [5:0] data_b

该博客探讨了如何使用Verilog设计一个时序逻辑电路,将连续输入的6个单bit数据转换为6bit并行输出。电路采用valid-ready和valid-only握手协议,并详细解释了如何处理数据延迟和计数器在数据拼接中的作用。文章通过两种解法阐述了设计思路,强调了在valid_a下降沿存储数据以及在cnt=5时确保正确拼接的重要性。

该博客探讨了如何使用Verilog设计一个时序逻辑电路,将连续输入的6个单bit数据转换为6bit并行输出。电路采用valid-ready和valid-only握手协议,并详细解释了如何处理数据延迟和计数器在数据拼接中的作用。文章通过两种解法阐述了设计思路,强调了在valid_a下降沿存储数据以及在cnt=5时确保正确拼接的重要性。

订阅专栏 解锁全文

订阅专栏 解锁全文

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?