描述

题目描述:

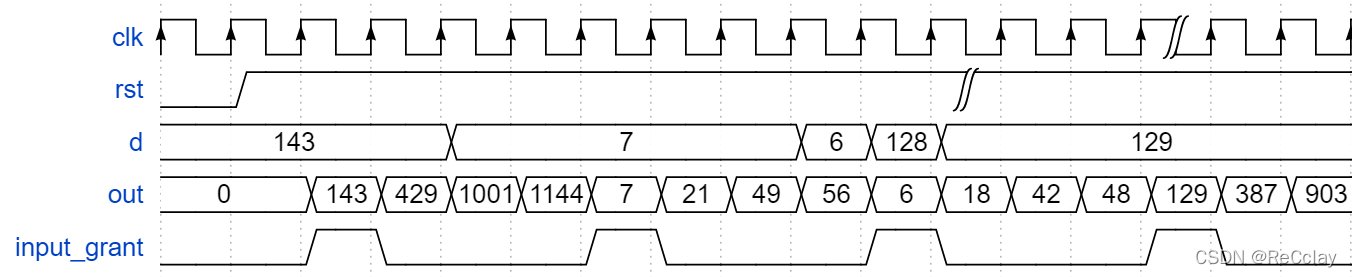

已知d为一个8位数,请在每个时钟周期分别输出该数乘1/3/7/8,并输出一个信号通知此时刻输入的d有效(d给出的信号的上升沿表示写入有效)

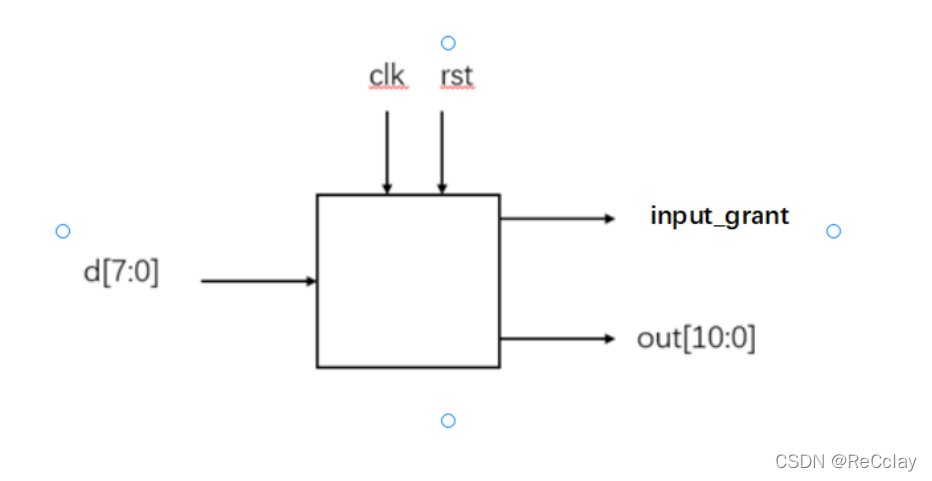

信号示意图:

波形示意图:

输入描述:

输入信号 d, clk, rst

类型 wire

在testbench中,clk为周期5ns的时钟,rst为低电平复位

输出描述:

输出信号 input_grant out

类型 reg

题解

题意整理

1、在硬件中进行乘除法运算是比较消耗资源的一种方法,想要在不影响延迟并尽量减少资源消耗,必须从硬件的特点上进行设计。根据寄存器的原理,由于是二进制,所以进位和退位为x2或者/2,同样除7可以使用进位3然后减去本身的做法,这样就将乘除法运算转化为位运算,这是一种比较简单的整数运算处理。

这篇博客介绍了如何使用Verilog进行数字集成电路设计,特别是针对8位数的乘法和移位运算。通过理解硬件资源的利用,将乘除法转换为位操作,降低资源消耗。内容包括设计一个状态机来处理输入信号,并在特定时钟沿锁存数据,以及如何实现乘1/3/7/8的效果。适合校招和数字IC设计初学者阅读。

这篇博客介绍了如何使用Verilog进行数字集成电路设计,特别是针对8位数的乘法和移位运算。通过理解硬件资源的利用,将乘除法转换为位操作,降低资源消耗。内容包括设计一个状态机来处理输入信号,并在特定时钟沿锁存数据,以及如何实现乘1/3/7/8的效果。适合校招和数字IC设计初学者阅读。

订阅专栏 解锁全文

订阅专栏 解锁全文

708

708

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?