文章目录

- 一、数据突发长度(burst length)

- 二、不同场景的最小FIFO深度

-

- 2.1、场景1:fa>fb with no idle cycles in both write and read

- 2.2、场景2:fa>fb with two clock cycle delay between two successive read and write

- 2.3、场景3:fa > fb with idle cycles in both write and read

- 2.4、场景4:fa > fb with duty cycles given for wr_enb and rd_enb.

- 2.5、场景5:fa < fb with no idle cycles in both write and read

- 2.6、场景6:fa < fb with idle cycles in both write and read

- 2.7、场景7:fa = fb with no idle cycles in both write and read

- 2.8、场景8:fa = fb with idle cycles in both write and read

- 2.9、场景9:Data rates are given,read and write random(important!!!)

- 三、总结

- 四、真题

- 参考

数字IC设计中我们经常会遇到这种场景,工作在不同时钟域的两个模块,它们之间需要进行数据传递,为了避免数据丢失,我们会使用到FIFO。当读数据的速率小于写数据的速率时,我们就不得不将那些还没有被读走的数据缓存下来,那么我们需要开多大的空间去缓存这些数据呢?缓存开大了会浪费资源,开小了会丢失数据,如何去计算最小FIFO深度是我们讨论的重点。

一、数据突发长度(burst length)

在讲解如何去计算FIFO深度之前,我们来理解一个术语burst length,如果你已经了解了可以跳过。要理解数据的突发长度,首先我们来考虑一种场景,假如模块A不间断的往FIFO中写数据,模块B同样不间断的从FIFO中读数据,不同的是模块A写数据的时钟频率要大于模块B读数据的时钟频率,那么在一段时间内总是有一些数据没来得及被读走,如果系统一直在工作,那么那些没有被读走的数据会越累积越多,那么FIFO的深度需要是无穷大的,因此只有在突发数据传输过程中讨论FIFO深度才是有意义的。也就是说我们一次传递一包数据完成后再去传递下一包数据,我们把一段时间内传递的数据个数称为burst length。在维基百科中,burst transmission是这样解释的:<

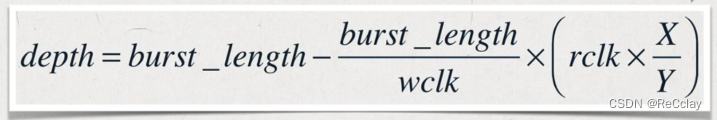

本文详细探讨了在数字IC设计中计算FIFO最小深度的重要性,特别是在不同场景下,如fa>fb、fa<fb和fa=fb的情况,并通过实例计算了9种不同场景下的最小FIFO深度。关键在于理解数据突发长度和计算未被读走的数据个数。最后,文章提供了FIFO深度的计算公式并给出了实际工程设计中的真题案例。

本文详细探讨了在数字IC设计中计算FIFO最小深度的重要性,特别是在不同场景下,如fa>fb、fa<fb和fa=fb的情况,并通过实例计算了9种不同场景下的最小FIFO深度。关键在于理解数据突发长度和计算未被读走的数据个数。最后,文章提供了FIFO深度的计算公式并给出了实际工程设计中的真题案例。

订阅专栏 解锁全文

订阅专栏 解锁全文

5275

5275

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?