一、逻辑门单元

逻辑门单元是实现基本逻辑运算和符合逻辑运算的单元电路。逻辑门单元分为组合逻辑门单元和时序逻辑门单元两种。

时序分析中逻辑门延时和信号线延时是计算延时的主要组成部分,如下图所示。

逻辑门延时定义为逻辑单元自身逻辑求值的时间。信号线延时的定义为逻辑信号从逻辑门单元的输出端口开始在互联线上传播到下一级逻辑输入端口的延时。

二、门单元的时序计算参数

静态时序分析中,需要通过提取逻辑门单元相关的时序参数的数值来验证设计在时序上的正确性。组合逻辑门单元相关的时序参数主要包括信号转换延时和逻辑门延时。

1.信号转换延时:输入端口或者输出端口的信号电平由高电平转换成低电平,或者由低电平转换成高电平所需要的时间即为信号转换延时。

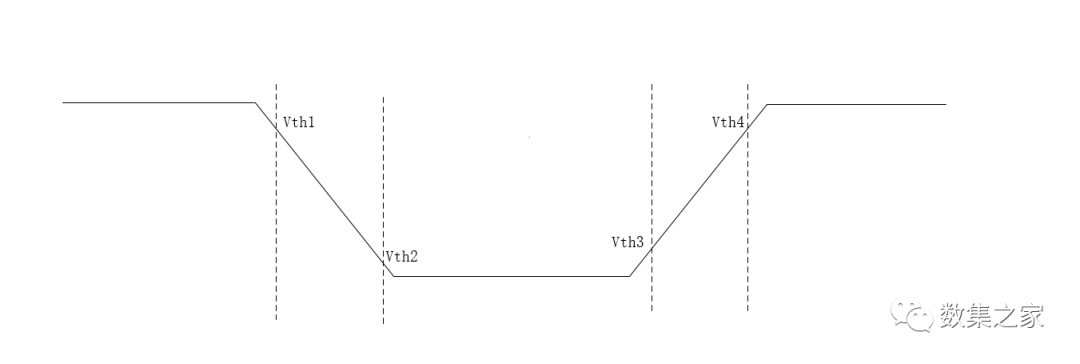

如下图所示,信号的有效高电平值通过定义阈值电压Vth1和Vth4来界定,而低电平值通过定义阈值电压Vth2和Vth3来界定。

本文介绍了静态时序分析(STA)的基础知识,重点讨论逻辑门单元的分类及在时序分析中的作用。内容包括逻辑门延时和信号线延时的定义,以及在STA中如何计算门单元的时序参数,如信号转换延时和逻辑门延迟。通过阈值电压和信号变化百分比来设定参数,确保设计的时序正确性。

本文介绍了静态时序分析(STA)的基础知识,重点讨论逻辑门单元的分类及在时序分析中的作用。内容包括逻辑门延时和信号线延时的定义,以及在STA中如何计算门单元的时序参数,如信号转换延时和逻辑门延迟。通过阈值电压和信号变化百分比来设定参数,确保设计的时序正确性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

9159

9159