时钟特性

在同步电路设计中,各功能逻辑单元之间的数据传输都由一个同步信号控制,这个执行统一指挥的信号就是时钟信号。

时钟的时序特性主要分为时钟周期、时钟占空比、时钟转换时间、时钟延迟、时钟偏斜和时钟抖动。

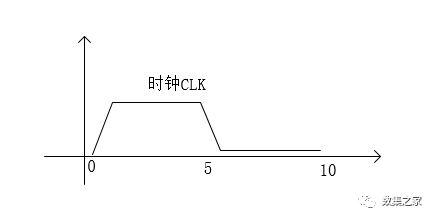

1.时钟周期

时钟周期也称为震荡周期,定义为频率的倒数,如下图所示为一个周期为10的时钟信号波形。

静态时序分析中需要设置时钟周期即时钟信号的工作频率,作为时序参考基础,来检查时序路径是否满足时序要求。

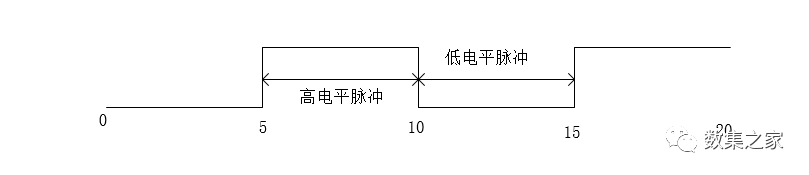

2.时钟占空比

时钟占空比是指时钟信号高电平在一个周期之内所占的时间比率。一般设计中,大部分的时钟占空比为50%,即占空比为0.5,说明高、低电平所占时间都为0.5个周期。但根据设计的需要,也可以设计占空比不同的时钟信号。

3.时钟转换时间

理想情况下,时钟信号在不同电平之间进行切换是不需要时间的,但是实际时钟信号在不同电平之间切换时,由于供电电压、工艺变化、扇出负载大小等因素,是需要转换时间的。

时钟转换时间一般定义为时钟信号的电压从标准供电电源电压的10%变化到标准供电电源电压的90%的时间间隔。根据设计的不同需要,设计者可以通过单元时序计算参数来定义不同

本文详细介绍了同步电路设计中的时钟特性,包括时钟周期、时钟占空比、时钟转换时间、时钟延迟、时钟偏斜和时钟抖动。时钟周期是时序分析的基础,时钟占空比通常为50%,时钟转换时间和延迟影响信号质量,时钟偏斜和抖动则会带来时序不确定性。理解这些概念对于静态时序分析至关重要。

本文详细介绍了同步电路设计中的时钟特性,包括时钟周期、时钟占空比、时钟转换时间、时钟延迟、时钟偏斜和时钟抖动。时钟周期是时序分析的基础,时钟占空比通常为50%,时钟转换时间和延迟影响信号质量,时钟偏斜和抖动则会带来时序不确定性。理解这些概念对于静态时序分析至关重要。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2601

2601

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?