在同步电路当中,数据和时钟总是有着固定的关系,所以当这种关系在满足器件的建立和保持时间的要求时,输出就会在一段延时之后输出一个稳定的值。在同步电路中,满足时序要求的电路是不会有亚稳态出现的。但是,在异步电路中,由于数据和时钟有着不固定的关系,当这种关系违背了时序要求的时候,就会出现亚稳态。

亚稳态是由于违背了触发器的建立时间和保持时间而产生的。设计中的每个触发器都有建立时间和保持时间的要求,也就是数据在有效沿的前后需要保持一段稳定的时间,才能保证触发器采集到的数据是稳定的,如果在这段时间内数据发生了变化,那么触发器的输出就会出现不稳定的情况,这种不稳定的情况会持续一段时间才能恢复稳定。

亚稳态窗口,也就是之前提到的数据要保持的时间,也就是说它的长度等于该触发器的建立时间和保持时间,如下图所示。

避免亚稳态

根据问题出现的条件,即出现违背建立时间和保持时间的情况。信号可能违背时序要求的条件如下:

1.输入信号是异步信号。

2.时钟偏移/摆动(上升或下降时间)高于容限值。

3.信号在两个不同频率或者相同频率但是相位和偏移不同的时钟域下跨时钟域工作。

4.组合延迟使触发器的数据输入在亚稳态窗口内发生变化。

最简单的避免亚稳态的方法就是使时钟周期的长度足够长,这个时钟周期最小也要大于保持和建立时间以及通往下一级的触发器的路径上的任何延时。在大多数现代化设计的性能要求下,这种方法并不实用。

另一种避免亚稳态的方法是使用同步器。

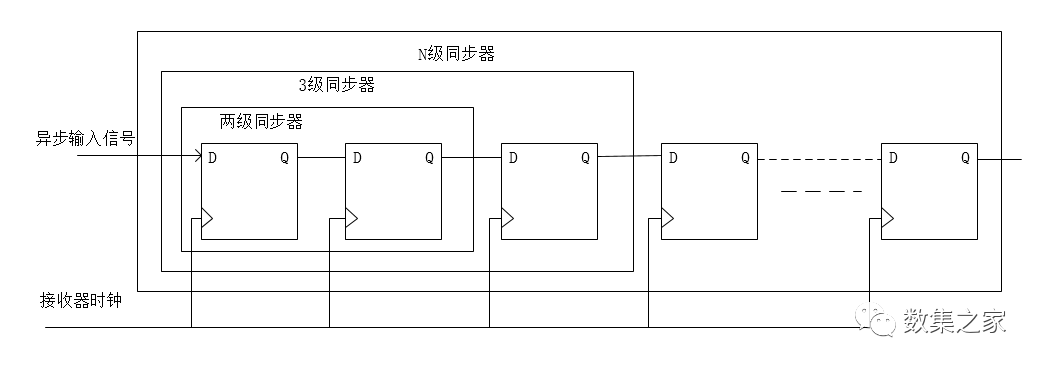

1.使用多级同步器

前面说过如果信号进入亚稳态,那么需要一定的时间恢复,所以可以在跨时钟域的信号上加上一个或者多个同步触发器,如下图所示。这样当第一级触发器发生亚稳态时,在后面的触发器只要经过这段时间,就能使信号恢复正常。但是这样的方式有个缺点,那便是会增加同步逻辑输入的延迟。

2.使用时钟倍频电路的多级同步器

上面提到多级同步器会导致同步逻辑输入延迟,系统需要花费较长的时间去响应异步输入。为了解决这个问题,可以用倍频时钟作为同步时钟的时钟输入,这种方法不仅能够缩短异步输入的响应时间,而且能够降低发生亚稳态的概率。

以上两种方法都不能保证亚稳态能不传播下去,但是能减少亚稳态发生的概率。

亚稳态检测电路

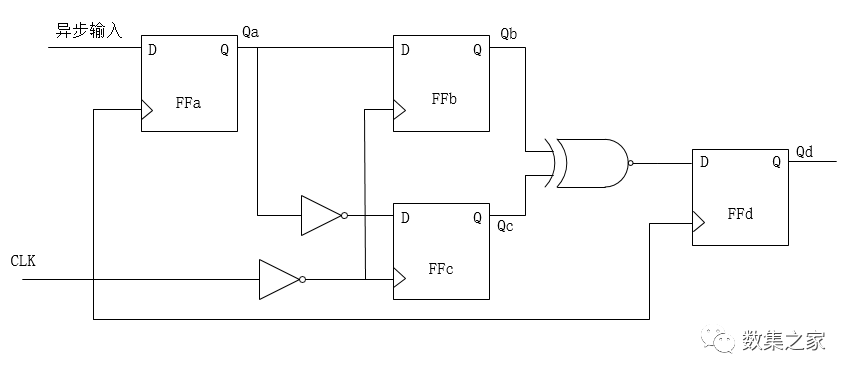

为了确定触发器的亚稳态特征,可以设计如下亚稳态检测电路。

当出现亚稳态的时候,两个互补输出Qb和Qc信号,经过同或门,然后输出。因为出现了亚稳态,那么Qd会输出高电平。如果没有出现亚稳态,同或门的输出应该是低电平,因为互补信号不管谁是0谁是1,都会输出低电平。只有当亚稳态出现的时候,同或门的输入的互补信号不再互补,所以输出高电平。

同步器类型

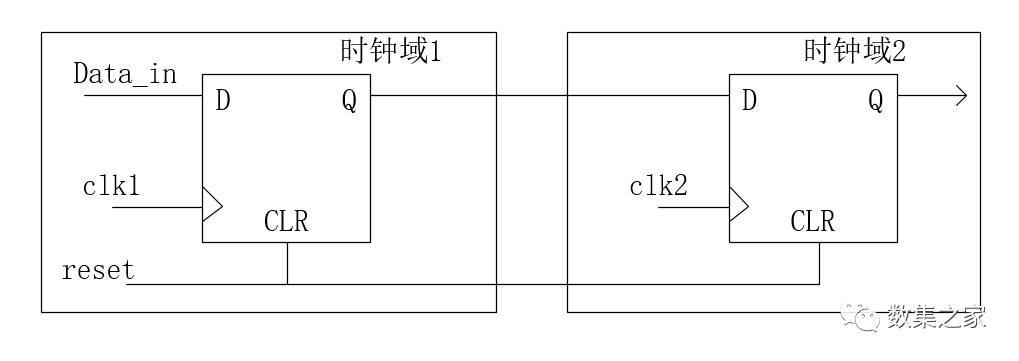

这里介绍两种模式的同步器,当异步输入信号比时钟周期要大得多的时候模式A的电路最有效,图示如下。

当输入的数据比时钟周期要大,也就是说总有有效沿能够采集到有效数据,而当亚稳态需要超过不只一个时钟周期才能恢复,那么需要级联更过的触发器。

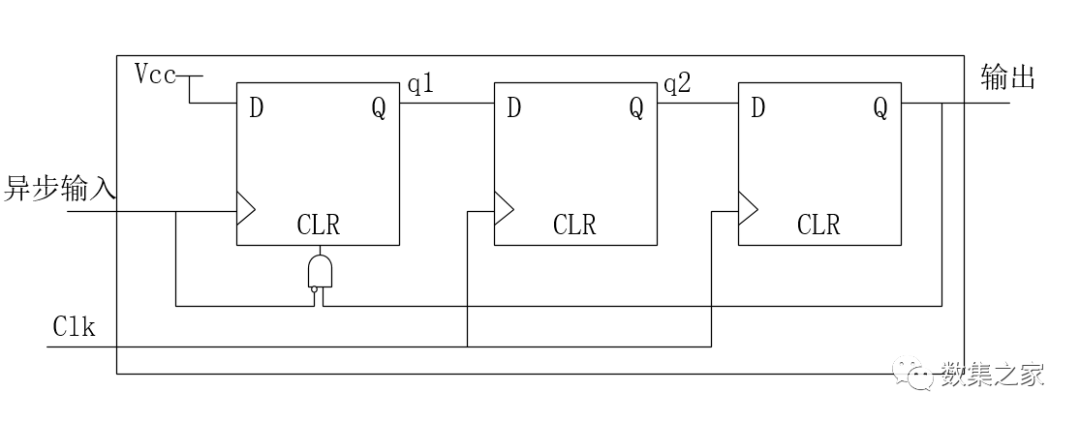

在异步输入信号的宽度小于时钟周期的时候,需要采用模式B的电路,图示如下。

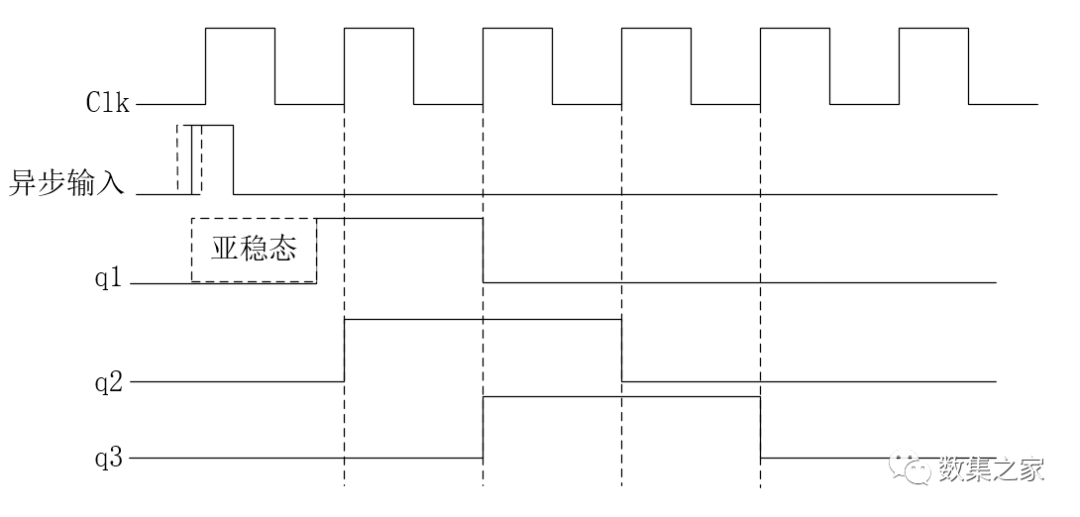

第一级触发器的输入端口D与Vcc相连,其时钟输入为异步输入信号。其波形图如下所示。

异步输入的短脉冲让q1变成高电平,这个高电平经过两个时钟之后从第三级触发器输出。

同步电路亚稳态问题及解决方法

同步电路亚稳态问题及解决方法

亚稳态在异步电路中由于违背时序要求产生,导致触发器输出不稳定。通过延长时钟周期、使用多级同步器或时钟倍频电路可降低其发生。亚稳态检测电路用于检测触发器的亚稳态特性,同步器类型分为模式A和模式B,适应不同输入信号宽度。

亚稳态在异步电路中由于违背时序要求产生,导致触发器输出不稳定。通过延长时钟周期、使用多级同步器或时钟倍频电路可降低其发生。亚稳态检测电路用于检测触发器的亚稳态特性,同步器类型分为模式A和模式B,适应不同输入信号宽度。

1022

1022

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?