研发阶段的信号完整性(SI)分析是确保高速信号(>100MHz)稳定传输的核心,直接影响 PCB 的功能与可靠性。

:从 “反射” 到 “串扰” 的根源解析

四层板研发中需聚焦三大 SI 问题,PCB 四层板厂家的实践揭示关键机理:

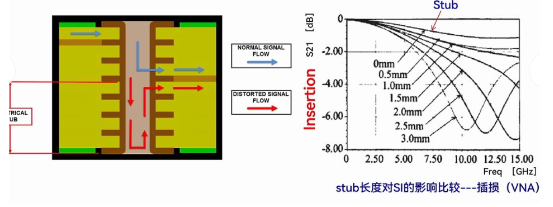

信号反射的 “阻抗失配”。当信号传输线阻抗(如 50Ω)与负载阻抗不匹配时,会产生反射(反射系数 ρ=|Z2-Z1|/|Z2+Z1|),1GHz 信号在阻抗偏差 20% 时,反射损耗从 - 20dB 恶化至 - 14dB,导致眼图闭合。某四层板的 1.5GHz 信号分析显示,0.15mm 线宽的传输线因过孔寄生电感(0.5nH),阻抗从 50Ω 升至 60Ω,反射损耗达 - 16dB,增加接地过孔后阻抗回调至 52Ω,损耗改善至 - 22dB。

串扰的 “耦合干扰”。平行布线的高速信号会通过电容(互容)和电感(互感)产生串扰,0.15mm 线宽、0.12mm 间距的 50mm 平行线段,1GHz 信号的串扰可达 - 28dB(允许值 - 30dB),超出设计阈值。某四层板的分析显示,数字信号(3.3V)与模拟信号(5mV)并行布线时,串扰导致模拟信号噪声增加 15mV,远超 ADC 的噪声容限(10mV),通过 “接地隔离带 + 差分对布线” 后,串扰降至 - 45dB,噪声控制在 3mV 以内。

时序偏移的 “数据错误”。高速信号(如 DDR4,2400Mbps)的时序偏差(建立 / 保持时间不足)会导致数据采样错误,某四层板的分析发现,100mm 长的信号路径因延迟差异(50ps)超出时序预算(30ps),通过等长布线(误差<5mm)将延迟差缩至 20ps,满足设计要求。此外,温度变化(-40℃至 125℃)会使信号延迟变化 ±10%,研发阶段需通过仿真验证极端温度下的时序裕量(需>20%)。

从 “仿真” 到 “测试” 的闭环验证

研发阶段的 SI 分析需结合仿真与测试,实践方案如下:

仿真工具的 “精准预测”。采用 HyperLynx 或 Cadence Allegro 进行全波仿真,建模时需包含四层板的实际叠层参数(如 FR-4 的 Dk=4.2±0.2,介质厚度 0.15mm),确保仿真精度(与实测偏差<10%)。某四层板的仿真显示,未优化的差分对(USB3.0)在 10GHz 时眼图张开度仅 60%,调整线长差(<5mm)和间距(0.2mm)后,眼图张开度提升至 85%,完全满足协议要求。仿真需重点验证关键网络:时钟信号(反射损耗、抖动)、差分对(等长、阻抗)、高速数据总线(串扰、时序)。

测试验证的 “结果校准”。制作测试 coupon(含传输线、过孔、差分对等结构),通过矢量网络分析仪(VNA)测试阻抗(50Ω±2Ω)、插入损耗(10GHz 下<0.8dB/cm)和串扰(<-30dB),对比仿真数据校准模型。某 PCB 四层板厂家的测试显示,仿真的插入损耗(0.7dB/cm)与实测(0.75dB/cm)偏差 5%,通过修正介电常数(从 4.2 调至 4.3)使模型更精准。对于批量生产,测试 coupon 需随板制作,确保研发设计与量产工艺的一致性(偏差<3%)。

优化措施的 “针对性实施”。针对反射问题,可增加终端匹配(如串联电阻 50Ω),使反射损耗从 - 15dB 提升至 - 25dB;解决串扰需增加线间距(从 0.12mm 增至 0.2mm)或插入接地过孔(间距 5mm),串扰可降低 10-15dB。

常见分析误区与规避:PCB 四层板厂家的 “经验库”

研发阶段需避免三大错误,实践方案如下:

忽视低速信号的 SI 问题。虽 100MHz 以下信号反射影响较小,但串扰仍可能超标(如 50MHz 平行布线 50mm,串扰达 - 25dB),建议所有信号均做基础分析(至少检查串扰)。

仿真模型过度简化。忽略过孔、焊盘等细节导致仿真偏差,某四层板仿真未计入焊盘电容(0.5pF),使 1GHz 信号的反射预测值优于实测 10dB,添加细节后偏差缩至 3dB。

未考虑量产工艺波动。研发设计的线宽精度(±3μm)超出四层板量产能力(±5μm),导致量产阻抗偏差达 ±7Ω,建议设计时预留工艺余量(如目标阻抗 50Ω,设计按 48Ω)。

PCB 研发阶段的信号完整性分析,是高速电路设计的 “隐形防线”。PCB 四层板厂家捷配PCB的实践证明,通过仿真预测、测试验证和针对性优化,可使高速信号的可靠性提升 80%,为后续量产奠定坚实基础。

241

241

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?