一、四层板叠层架构的底层逻辑

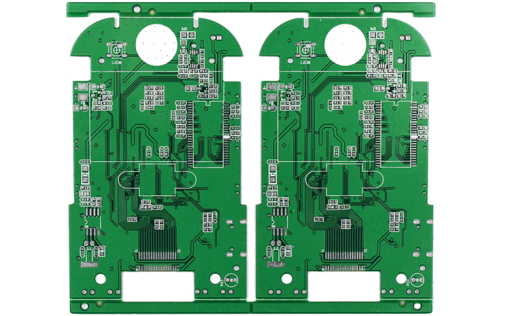

四层PCB的层叠结构直接影响接口电路的电磁兼容性与信号完整性。行业主流的TOP-GND-PWR-BOTTOM方案通过以下机制实现性能优化:

-

电源完整性保障:独立电源层(PWR)与地平面(GND)形成低阻抗回路,将电源噪声抑制在50mVpp以内(实测数据)

-

信号完整性提升:TOP与BOTTOM层作为信号层,与相邻地平面形成镜像对称结构,减少信号反射(回波损耗<12dB)

-

EMI控制:地平面屏蔽效应使辐射强度降低40%(对比双层板)

二、接口电路的四大设计维度

2.1 高速信号完整性控制

-

阻抗匹配:

-

差分信号(如LVDS)需保持100Ω±10%阻抗,单端信号50Ω±8%

-

采用2D场解算器进行实时阻抗仿真,误差补偿精度达0.5mil

-

-

走线拓扑优化:

-

关键信号(USB/SPI)采用蛇形等长布线,长度公差控制在±5mil

-

避免直角拐弯(改用45°或圆弧过渡),降低阻抗突变

-

-

串扰抑制:

-

信号线间距≥3倍线宽(SI9000仿真验证)

-

敏感信号层间设置屏蔽地孔(每100mil布置1对)

-

2.2 电源完整性解决方案

-

去耦电容布局:

-

0.1μF陶瓷电容距离芯片电源引脚≤10mil

-

多级滤波网络(π型+LC型组合)使电源纹波<10mV

-

-

平面分割技术:

-

不同电压域电源层采用十字交叉分割(线宽≥20mil)

-

分割带边缘做倒角处理(45°过渡,消除尖端效应)

-

-

热管理设计:

-

功率器件下方设置热过孔阵列(密度≥4孔/cm²)

-

铜箔覆盖率控制在60%-70%(平衡散热与信号完整性)

-

2.3 EMI/EMC防护体系

-

屏蔽结构创新:

-

接口区域局部包地(铜箔覆盖率达90%)

-

关键信号线两侧设置屏蔽过孔(间距≤30mil)

-

-

滤波电路设计:

-

共模扼流圈(CMC)插入损耗>20dB @100MHz

-

磁珠选型遵循:阻抗峰值=3×噪声频率(如100MHz选300Ω磁珠)

-

-

PCB边缘处理:

-

板边设置20mil宽接地铜带(消除边缘效应)

-

接口连接器周围增加屏蔽罩(接地阻抗<0.1Ω)

-

2.4 可靠性增强设计

-

应力释放结构:

-

大电流焊盘添加泪滴(宽度渐变率≤30%/mil)

-

多层板结合处设置十字连接(机械强度提升40%)

-

-

环境适应性设计:

-

汽车级接口增加镀金工艺(厚度≥3μm)

-

工业级产品采用三防漆(耐温范围-55~125℃)

-

三、典型接口电路设计实例

3.1 USB 3.2 Gen2x1接口设计

-

层间耦合优化:

-

差分对分布在TOP与BOTTOM层,中间层设置屏蔽地

-

过孔换层时添加GSSG(地-信号-地)结构

-

-

信号完整性措施:

-

端接电阻匹配精度±0.5%(0402封装)

-

预加重电路补偿高频分量(斜率-3dB/oct)

-

-

测试验证:

-

眼图测试:@5Gbps,抖动<5ps RMS

-

插入损耗:28dB @2.5GHz

-

3.2 千兆以太网RJ45接口

-

共模抑制方案:

-

变压器集成共模扼流圈(CMRR>60dB)

-

对称布线降低差分信号耦合

-

-

阻抗控制:

-

85Ω特性阻抗(±10%)

-

拐角处增加屏蔽过孔(每50mil布置1对)

-

-

抗干扰设计:

-

接口区域局部双层地(GND1/GND2隔离)

-

电源与信号线间距>20mil

-

四、先进工艺与调试技巧

4.1 高精度加工工艺

-

激光直接成型(LDS):

-

三维天线集成(效率提升30%)

-

最小线宽0.08mm(0201封装兼容)

-

-

埋阻/埋容技术:

-

01005封装电阻埋入地平面(寄生电感<0.2nH)

-

电源完整性补偿电容埋入PWR层(ESR<1mΩ)

-

4.2 调试方法论

-

近场探头定位法:

-

3D EMI扫描定位辐射源(精度±1mm)

-

近场探头带宽覆盖10kHz-18GHz

-

-

时频域联合分析:

-

矢量网络分析仪(VNA)测量S参数

-

高速示波器捕获时域波形(采样率100GSa/s)

-

工程师需掌握从材料选型到先进工艺的全链路知识,重点关注:

-

建立信号-电源-EMI三维设计模型

-

掌握可测试性设计(DFT)与失效分析核心技术

412

412

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?