一、基本组成

一个典型的锁相环(PLL)主要包含以下几个部分:

- 鉴相器(Phase Detector, PD):比较输入信号和反馈信号的相位差,输出一个反映相位误差的电压或数字信号。

- 环路滤波器(Loop Filter, LF):对鉴相器输出的误差信号进行滤波,产生一个平滑的控制电压。

- 压控振荡器(Voltage-Controlled Oscillator, VCO):振荡频率由环路滤波器输出的控制电压调节。

二、工作原理

- 相位比较:鉴相器检测参考时钟(输入信号)和反馈信号(经过分频的VCO输出)之间的相位差。

- 产生误差信号:相位差转换为电压或数字量,表示两信号相位的偏差大小和方向。

- 滤波平滑:环路滤波器滤除高频噪声,使误差信号平滑稳定,作为VCO的控制输入。

- 调整振荡频率:VCO根据控制电压调整频率,使反馈信号逐步靠近参考信号的频率和相位。

- 锁定状态:当反馈信号与参考信号相位差保持在一定范围内,PLL被“锁定”,输出信号频率和相位稳定且与参考信号同步。

三、一阶锁相环数学模型

建立一阶锁相环数学模型对后面的分析是很有帮助的

典型一阶锁相环结构包含:

- 鉴相器(Phase Detector, PD):输出与相位误差成正比的信号(简单模型下)

- 低通滤波器(LPF):一阶低通滤波器,简单时域模型就是积分器的理想低通响应,也可以是理想直通

- 数字控制振荡器(NCO):频率由输入控制电压(或者数字量)决定,频率积分成相位。

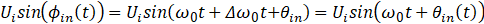

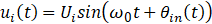

输入参考信号

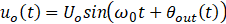

VCO输出信号

鉴相器:

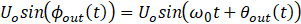

相位误差

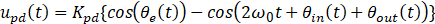

正弦鉴相器输出:

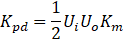

其中 Kpd 是鉴相器增益,单位是 V/rad。

是鉴相器增益,单位是 V/rad。

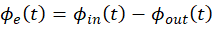

低通滤波器:

一阶系统

其中 是滤波器时间常数。

是滤波器时间常数。

分析时可以视为理想低通滤波器。

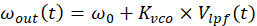

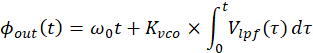

VCO:

VCO 可视为积分器件,在连续时间域,

所以,VCO的输出相位是:

其中 是振荡器增益(rad/s/V)。

是振荡器增益(rad/s/V)。

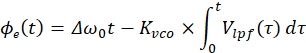

整理可得,

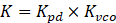

引入环路增益概念

环路增益通常指的是锁相环中整个环路(从鉴相器输出到控制振荡器频率变化的总增益)的大小。它是多个模块增益的乘积。

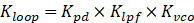

- 鉴相器增益 KPD (单位:V/rad 或 数字单位/rad)

- 环路滤波器增益KLPF(影响信号的幅度和相位)

- 压控振荡器增益 KVCO(单位:Hz/V 或 rad/sample/V)

环路增益一般表示为:

环路增益过高的影响

- 环路频率调整过快:环路增益过大时,系统对相位误差的响应非常敏感,VCO频率会剧烈变化,可能产生过冲。

- 系统振荡和不稳定:过高的增益使反馈环路的相位裕度变小,导致振荡、发散甚至失锁。

- 噪声放大:增益过大还可能放大噪声,导致输出抖动变大。

环路增益过低的影响

- 响应迟缓:系统对相位误差响应缓慢,锁定时间变长。

- 锁定能力下降:环路增益太小可能导致捕获范围和锁定范围缩小。

环路增益设置分析

由于

锁定状态

所以

其中,

四、工作过程

输入参考信号

VCO输出信号

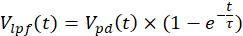

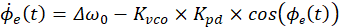

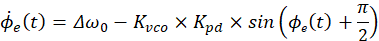

则鉴相器输出信号

其中, ,

, 为鉴相器增益,单位为/V。

为鉴相器增益,单位为/V。

经过低通滤波器后,输入VCO的信号近似为

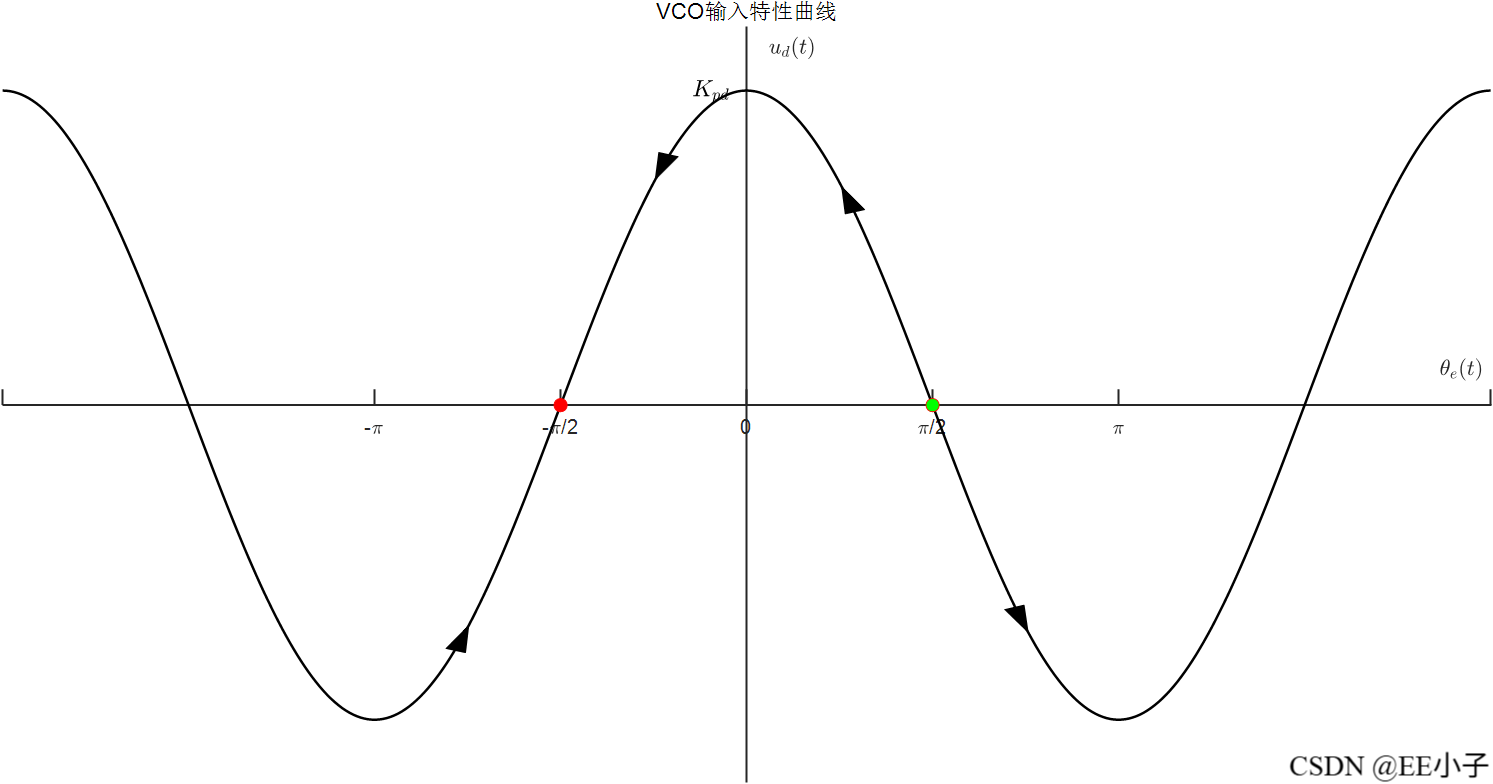

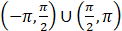

分析: 取值范围为

取值范围为 ,如图所示,此时取

,如图所示,此时取

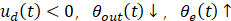

在 内,

内,

在 内,

内,

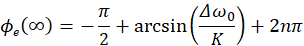

已知锁定状态 ,所以

,所以 为稳定锁定点,

为稳定锁定点, 为不稳定点。所以锁定后存在稳态相差

为不稳定点。所以锁定后存在稳态相差 。

。

举一反三可知,对于输入信号和输出信号分别为正弦或余弦形式,以及输入信号和输出信号存在初始频差的情况下,分析方法类似,不再赘述。

PLL原理详解与应用

PLL原理详解与应用

1634

1634

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?