文章目录

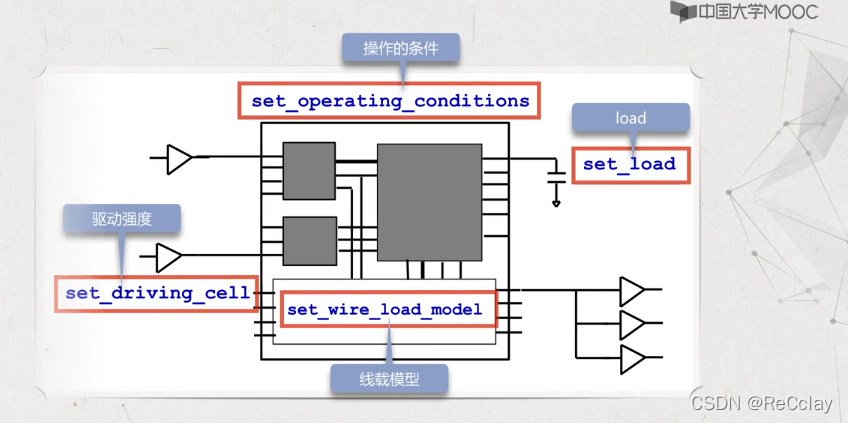

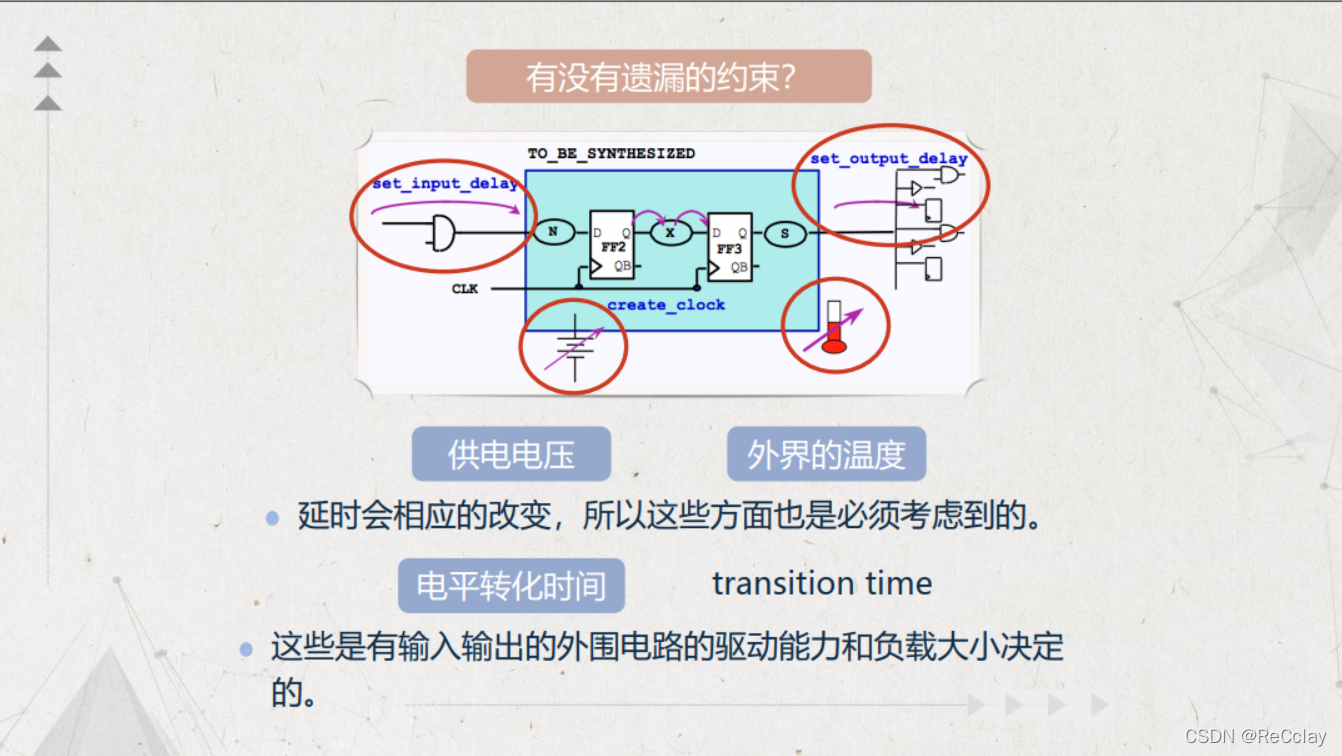

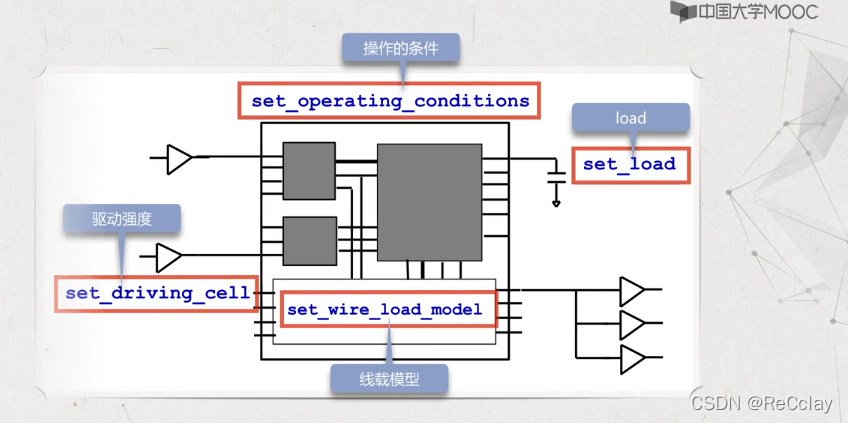

工作条件包括三方面的内容: 温度、电压以及工艺。单元的延时会随着温度的上升而增加;随着电压的上升而减小;随着工艺尺寸的增大而增大。 这些工作条件一般分为三种:最好情况(best case)、典型情况(typical case)以及最差情况(worst case)。 一般综合只要考虑到最差和最好两种情况,最差情况用于作基于建立时间 (setup time)的时序分析,最好情况用于作基于保持时间(hold time)的时序分析。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?