文章目录

一、 逻辑综合概述

1、 逻辑综合的专题学完之后,能够掌握以下五个核心知识点

- (1) 懂得为什么要逻辑综合;

- (2) 懂得逻辑综合的基本原理;

- (3) 懂得逻辑综合需要提供哪些文件;

- (4) 知道逻辑综合过程需要施加哪些约束;

- (5) 知道逻辑综合能够产生哪些结果。

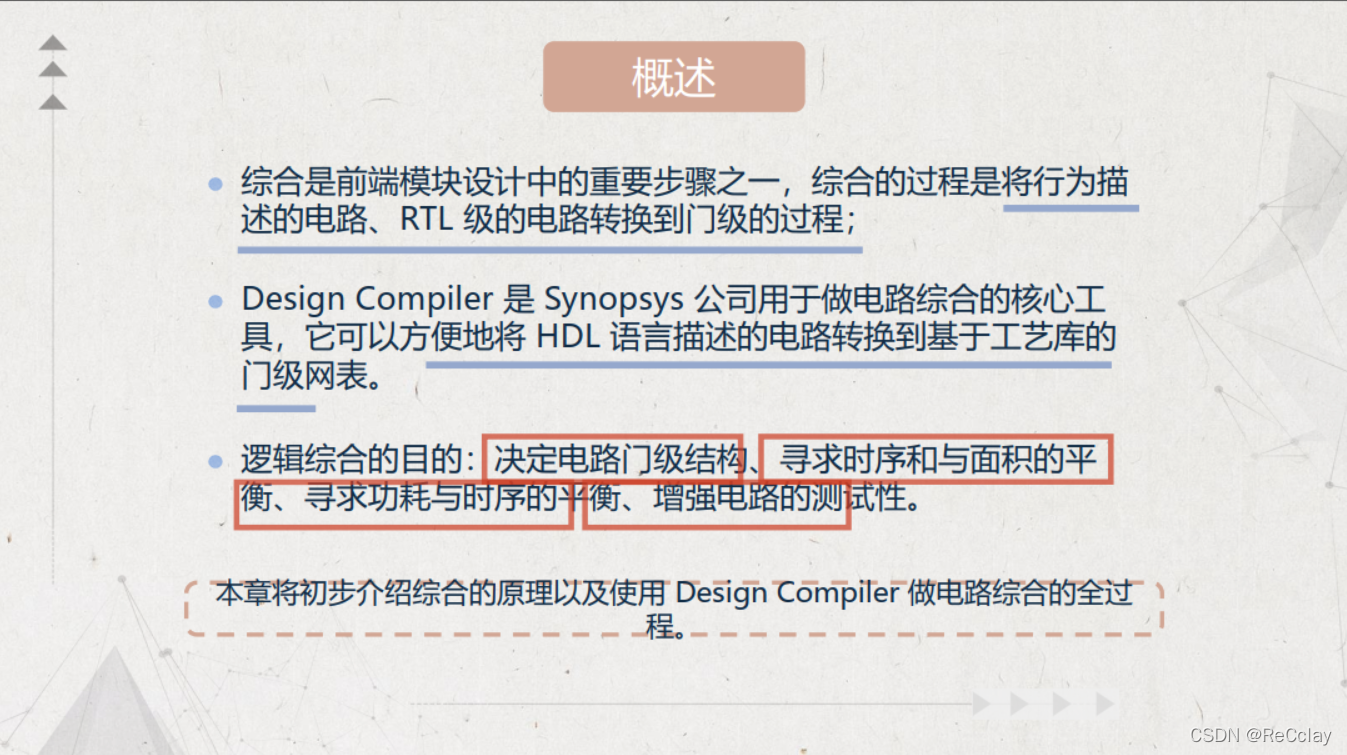

2、 逻辑综合是 ASIC 前端设计中的一个重要步骤:

- 综合的过程就是将抽象程度较高的 RTL 代码转换到与工艺库相关的门级网表的过程。

- 逻辑综合的目的是决定电路的门极结构,寻求面积与时序的平衡,寻求功耗与时序的平衡,增强电路的测试性。

- 逻辑综合主要的 EDA 工具是新思科技的 DesignCompiler。

本文介绍了逻辑综合的基础知识,包括其在ASIC前端设计中的重要性,主要步骤转译、优化和映射,以及关键对象如design、port、clock等。逻辑综合使用DesignCompiler工具,目标是实现面积、时序和功耗的平衡。同时,文章强调了设计约束的清晰定义以避免命名冲突,并概述了静态时序分析在检查建立时间和保持时间中的作用。

本文介绍了逻辑综合的基础知识,包括其在ASIC前端设计中的重要性,主要步骤转译、优化和映射,以及关键对象如design、port、clock等。逻辑综合使用DesignCompiler工具,目标是实现面积、时序和功耗的平衡。同时,文章强调了设计约束的清晰定义以避免命名冲突,并概述了静态时序分析在检查建立时间和保持时间中的作用。

订阅专栏 解锁全文

订阅专栏 解锁全文

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?