边沿检测主要作用是能够准确的识别出单比特信号的上升沿或下降沿,也就是我们希望当上升沿或下降沿来到时,能够产生一个唯一标识上升沿或下降沿的脉冲信号来告诉我们上升沿或下降沿来了,我们就可以根据这个脉冲信号作为后续电路功能的启动。

上升沿检测

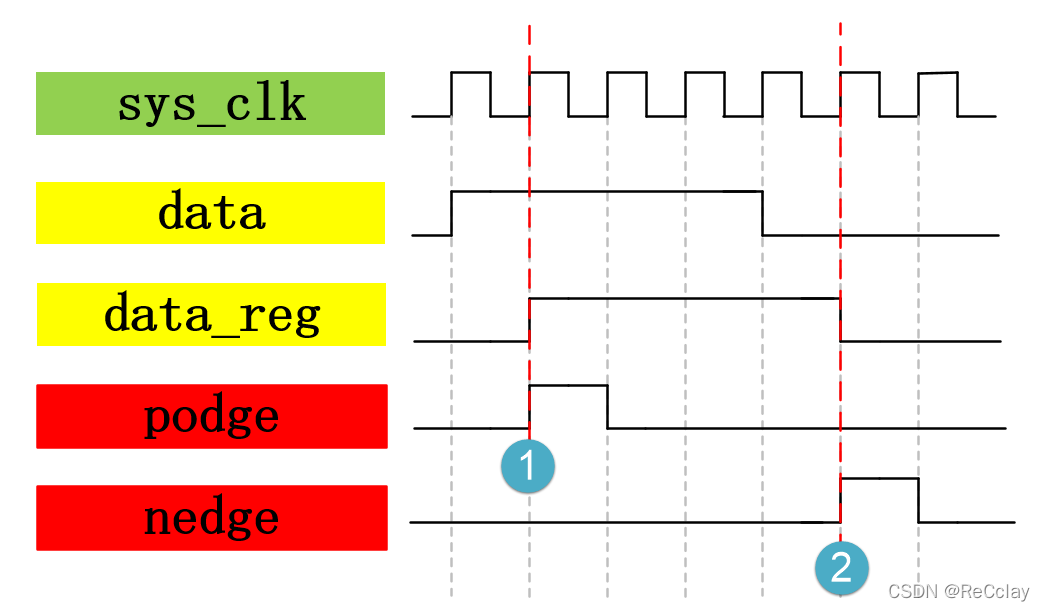

如下图所示,我们对同一信号打一拍后在①位置处就可以检测到上升沿,使之拉高一个时钟的脉冲;在②位置处可以检测到下降沿,使之拉高一个时钟的脉冲。要实现这个功能,我们该如何编写代码呢?

上升沿检测核心代码:在①处检测到 data 为高电平且 data_reg 为低电平时,表示有上升沿产生。

方法一: 与逻辑实现

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n ==

本文介绍了如何使用Verilog进行边沿检测,包括上升沿和下降沿的检测方法,分别通过与逻辑和或逻辑实现。核心逻辑是检测数据信号与寄存器信号的电平变化,产生相应脉冲信号,用于触发后续电路功能。同时提到了组合逻辑assign的实现方式,可提前一拍检测到边沿。

本文介绍了如何使用Verilog进行边沿检测,包括上升沿和下降沿的检测方法,分别通过与逻辑和或逻辑实现。核心逻辑是检测数据信号与寄存器信号的电平变化,产生相应脉冲信号,用于触发后续电路功能。同时提到了组合逻辑assign的实现方式,可提前一拍检测到边沿。

订阅专栏 解锁全文

订阅专栏 解锁全文

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?