【致读者】

您好!本文将通过一个 "AXI VIP + AXI BRAM" 的完整实战案例,手把手带您掌握AXI Verification IP的核心用法。为方便同行交流,我创建了一个硬件技术交流群,群内聚焦:

FPGA技术分享

实战问题讨论与答疑

行业动态与职业发展交流

若您对本专题感兴趣,欢迎私信我 “FPGA” 加入群聊

————————————————

一 引言

理论总是略显抽象,实战方能洞悉精髓。在上一篇《FPGA验证利器:全方位解析AXI Verification IP (AXI VIP)》系统介绍AXI VIP之后,本文将通过一个零基础、可复现的实战案例——使用AXI VIP驱动AXI BRAM——来让你真正上手。我们将从Vivado工程创建开始,一步步完成IP核集成、Testbench编写、TCL脚本控制以及协议检查,让你亲身体验AXI VIP带来的验证高效率与高可靠性。

二 实战平台搭建

接下来我们搭建一下AXI_VIP+BRAM的工程,来带大家详细了解一下AXI_VIP的用法。

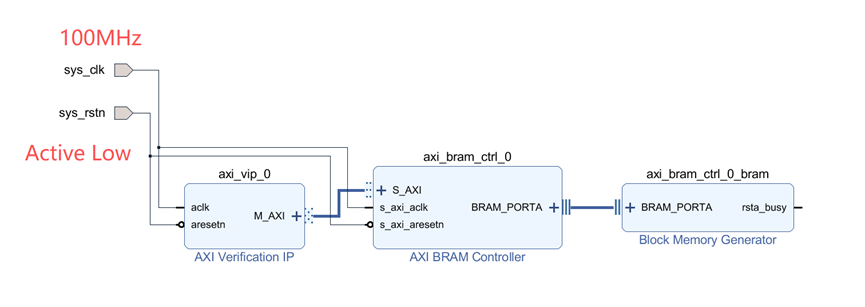

搭建的环境如下:外部输入时钟使用100MHz,复位使用rstn。

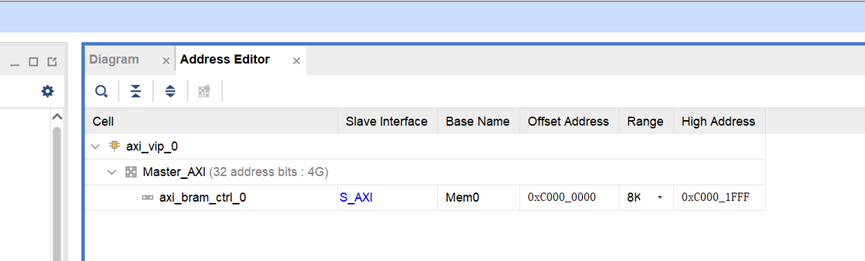

AXI_VIP通过0xC000_0000~0xC000_1FFF的地址对BRAM进行访问,即可以将数据写入BRAM中,并从BRAM中读取数据。

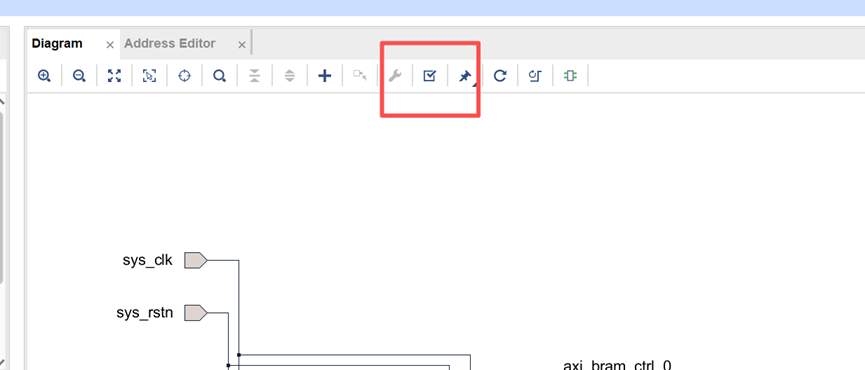

点击Validate Design对搭建的BlockDesign进行编译,编译无误。

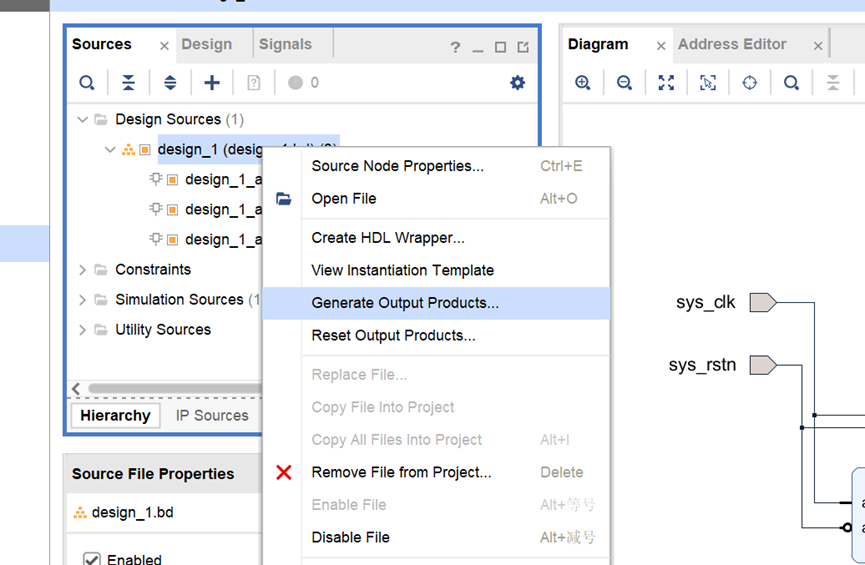

右键选择Generate Outout Products对内部所有的IP核进行编译。

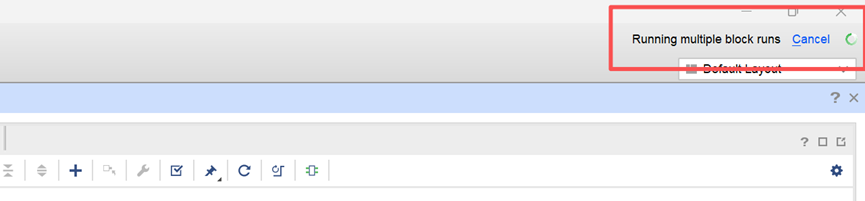

右上角显示的是编译中,等待编译完成绿圈就会停止转动

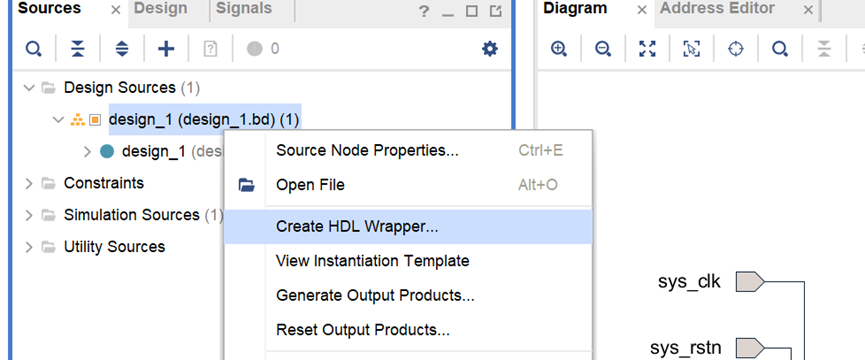

编译完成之后右键选择Create HDL Wrapper

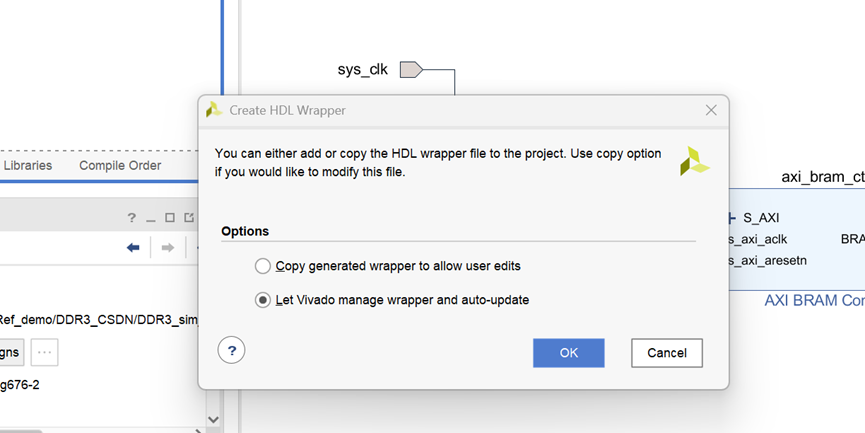

点击OK

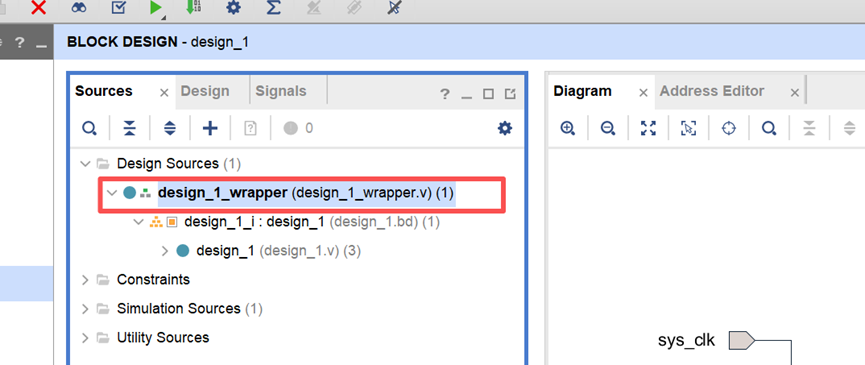

生成一个design_1_wrapper,也就是咱们常说的wrapper文件,这个之后就作为我们Block Design的顶层文件。

三 仿真文件编写

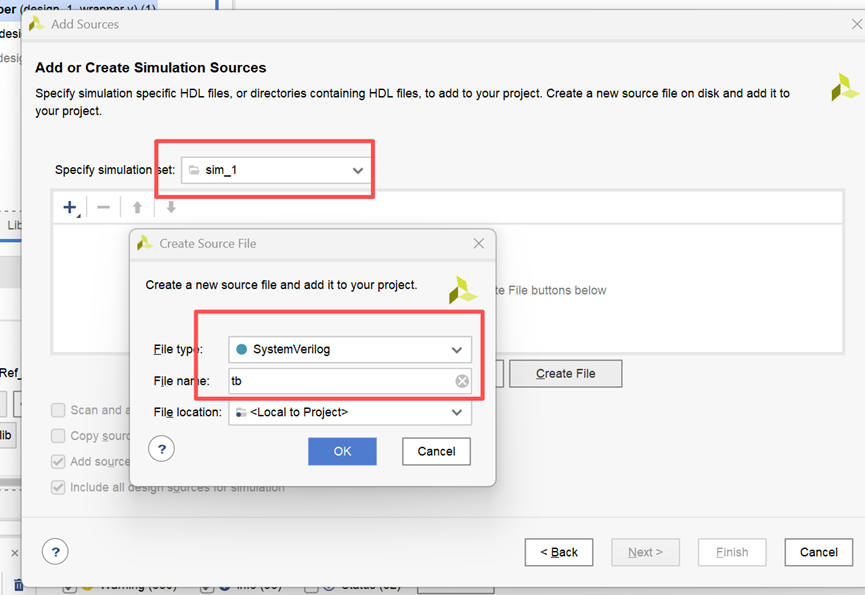

从这里开始编写仿真文件(tb),这里需要注意,文件类型需要定义为.sv文件,才能识别AXI_VIP相关的库,如下,我们新建一个tb.sv的文件,用于仿真。

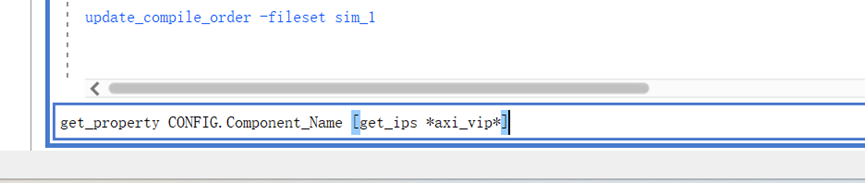

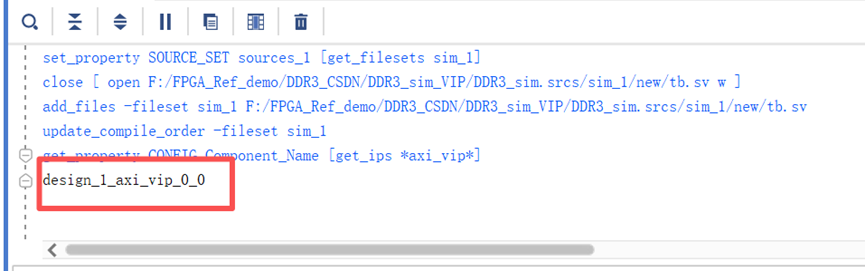

在tcl界面,输入如下指令获取VIP的名称

get_property CONFIG.Component_Name [get_ips *axi_vip*]

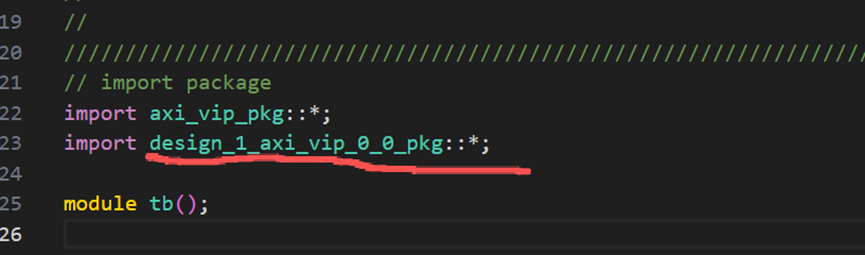

在tb文件前面标注import,导入对应的pkg库(必须是sv文件才行,v文件会报错的)

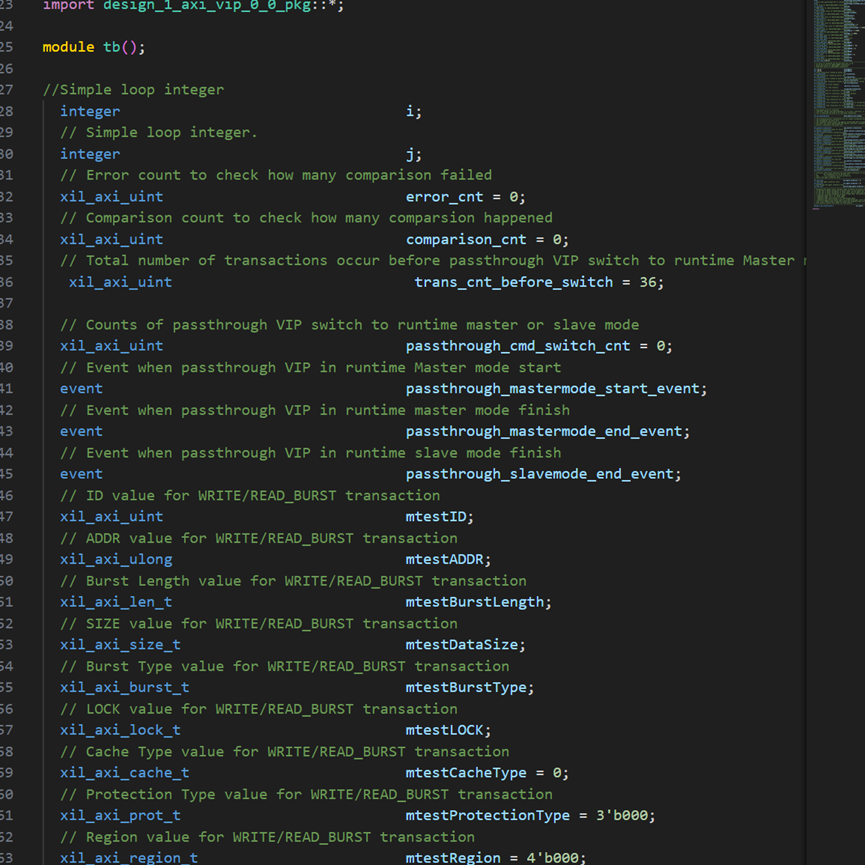

添加 定义的变量 ,从example中copy即可

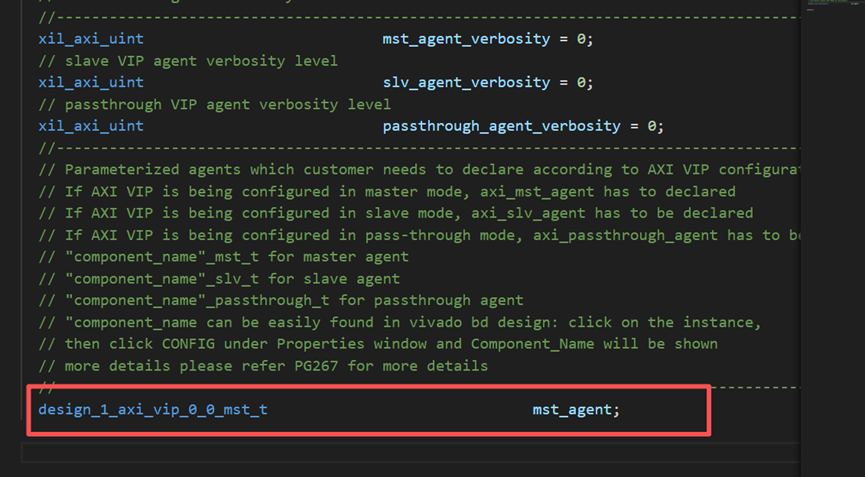

定义 mst_agent

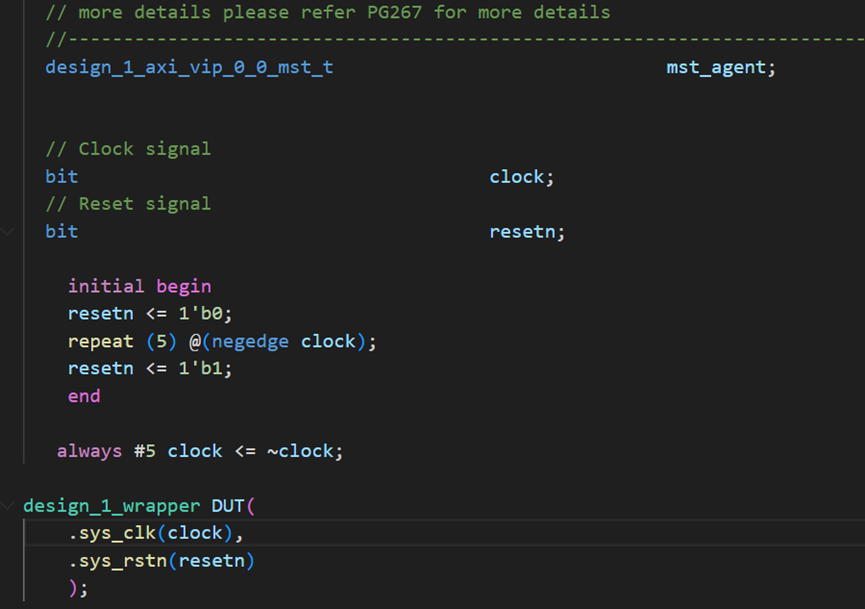

定义时钟和复位,例化wrapper模块

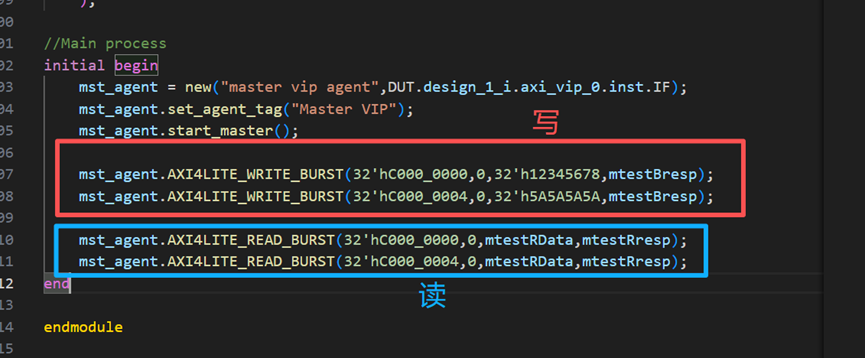

主逻辑如下:往0xC000_0000地址写入0x12345678 再往地址0xC000_0004地址写入0x5A5A5A5A

之后从这两个地址读出对应数据。

四 仿真结果解析

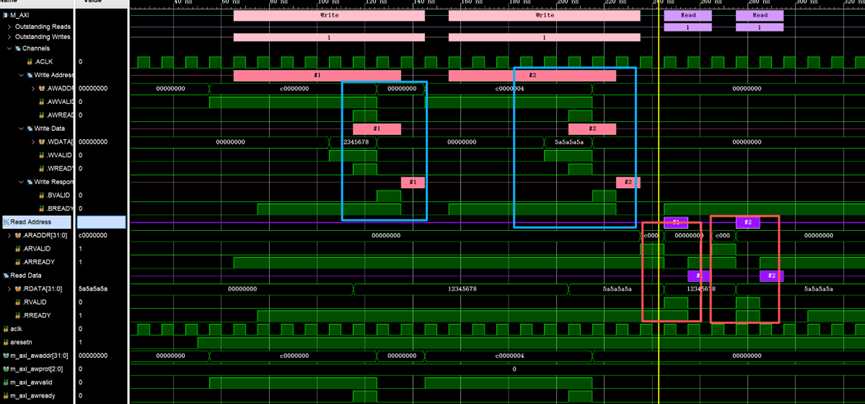

仿真结果如下,可以看出,发起了两笔写请求,

给0xc000_0000写入的值为0x12345678

给0xc000_0004写入的值为0x5A5A5A5A

之后又发起了两笔读请求

从0xc000_0000读取的值为0x12345678

从0xc000_0004读取的值为0x5A5A5A5A

读写结果一致。

总结与展望

通过这个看似简单但“五脏俱全”的实例,我们完整地走通了一个基于AXI VIP的验证流程:

-

平台搭建:集成AXI VIP与待测从设备。

-

环境配置:编写Testbench并添加仿真模型。

-

激励生成:使用TCL脚本高效控制VIP产生测试流量。

-

结果分析:通过波形验证功能与合规性。

你已经掌握了AXI VIP最基本也是最核心的使用方法。这为你接下来挑战更复杂的验证场景(例如:使用AXI VIP去驱动和验证MIG DDR3 IP核)奠定了坚实的地基。

在下一篇《FPGA DDR3工程级仿真:使用AXI VIP作为主设备驱动MIG IP核》 文章中,我们继续介绍使用AXI_VIP驱动DDR,欢迎大家关注点赞互动,谢谢大家!

4027

4027

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?