【致读者】

您好!在深入本篇关于 AXI Verification IP (AXI VIP) 的技术细节之前,我们想与您分享一个更重要的信息。为方便同行交流,我创建了一个硬件技术交流群,群内聚焦:

FPGA技术分享

实战问题讨论与答疑

行业动态与职业发展交流

若您对本专题感兴趣,欢迎私信我 “FPGA” 加入群聊

————————————————

一 引言

在复杂的FPGA系统中,AXI总线是连接各个IP核的“大动脉”。如何确保这片繁忙的交通网络高效、无误地运转?本文将带你深入探讨Xilinx官方出品的验证神器——AXI Verification IP (AXI VIP)。我们将通过实例解析其强大的协议检查与事务生成能力,为你构建一个清晰、系统的AXI VIP知识框架,为后续进行DDR3等高速接口的工程级验证打下坚实基础。

二 AXI VIP:为何是FPGA验证的“必需品”?

当我们对自定义的AXI主设备或从设备进行验证时,传统方法是手动编写测试平台(Testbench)。这种方式不仅效率低下,且极易因测试代码本身的错误而引入误导,更难以覆盖协议的所有边界情况。

AXI VIP的诞生,旨在解决三大核心痛点:

-

效率瓶颈:手动驱动复杂的AXI握手信号(

VALID/READY)繁琐且易错。 -

协议风险:肉眼检查波形难以发现细微的时序违规,为项目埋下“深水炸弹”。

-

场景局限:难以模拟真实世界中的各种极端情况(如随机背压、错误响应等)。

AXI VIP如同一位全能的“演员”、一位严格的“裁判”,和一位资深的“导演”,集三者于一身,能将你的验证工作提升到专业级水平。

三 核心架构解析:AXI VIP的三种工作模式

这是理解AXI VIP的基石。在创建VIP时,你必须首先选择其接口模式(Interface Mode),这决定了它在仿真中的角色和行为。

| 工作模式 | 角色定位 | 核心功能 | 典型应用场景 |

|---|---|---|---|

| MASTER | 流量发生器 | 模拟一个符合AXI协议的主设备,主动发起读写事务。 | 验证你设计的AXI从设备(如自定义寄存器模块、DMA控制器等)。 |

| SLAVE | 智能响应器 | 模拟一个从设备,根据配置对来自主设备的请求做出响应(可正常、可延迟、可报错)。 | 验证你设计的AXI主设备(如自定义图像处理引擎、DDR控制器等)。 |

| PASSIVE | 协议监视器 | 不驱动任何信号,仅被动监听AXI总线,检查事务是否符合协议规范。 | 在系统级仿真中,无侵入地监控任意AXI链路,用于协议合规性审计和性能分析。 |

理解这一点至关重要:你需要根据被测对象 来选择VIP的模式。若要测一个从设备,VIP就应配置为 MASTER 来向其发送流量;反之亦然。MASTER是我们测试最常用的模式。

四 实战准备:VIP的配置及使用说明

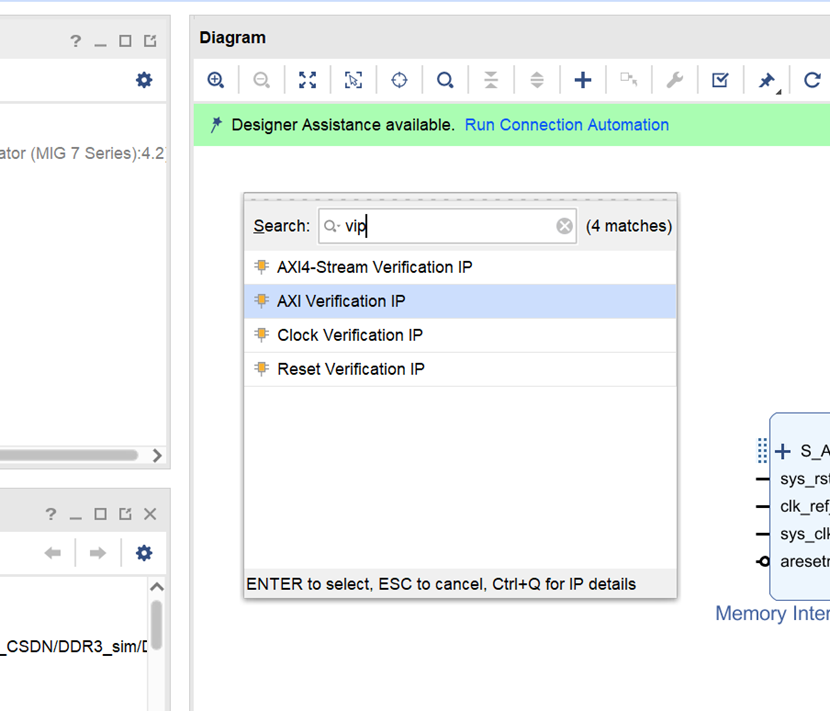

我们搜索VIP的ip核

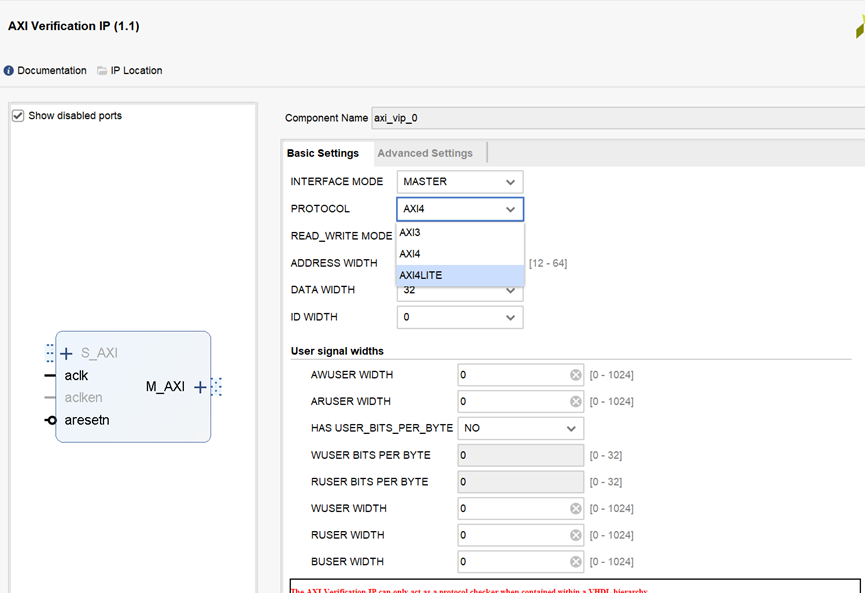

配置VIP为MASTER模式

选择协议使用AXI4LITE还是AXI4 FULL,我们本次使用AXI4LITE。

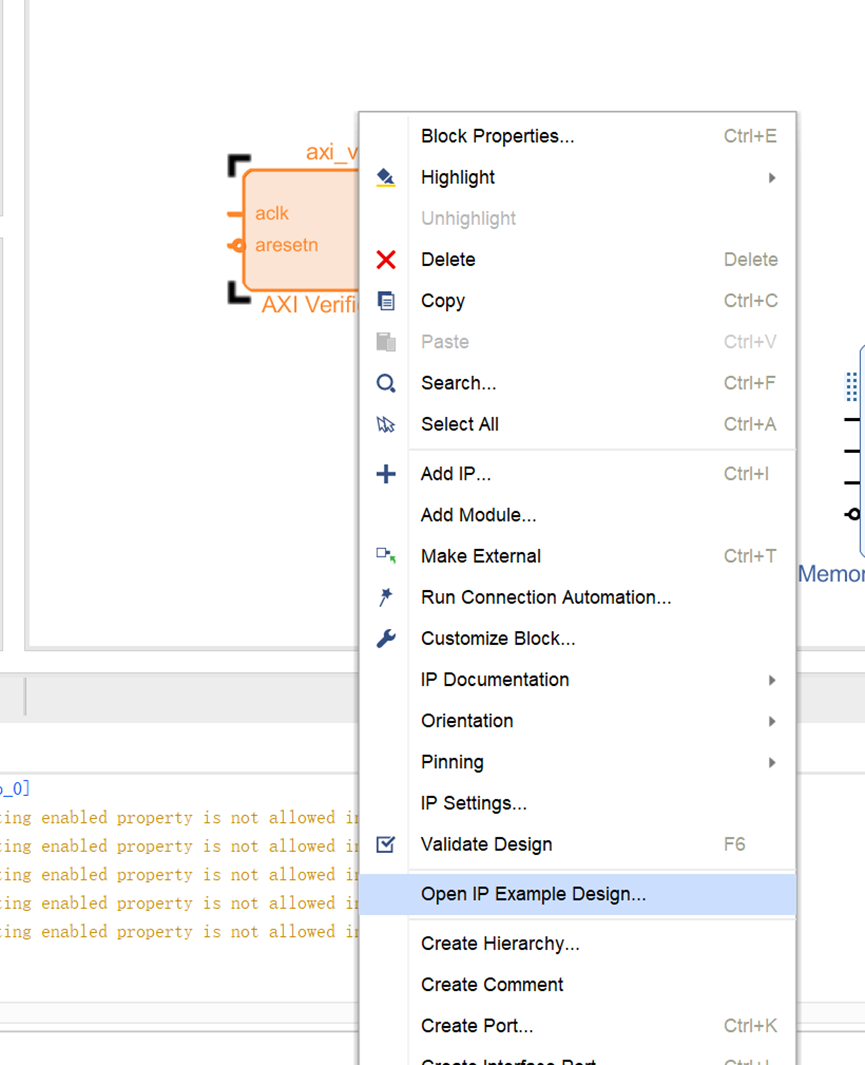

IP核生成好之后右键选择Open IP Example Design

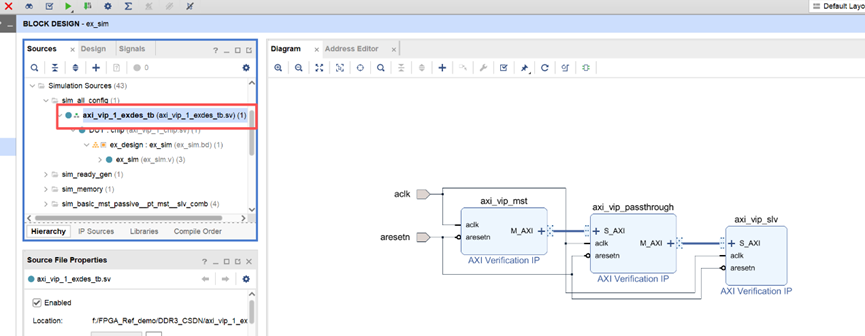

打开xilinx自带的示例如下,本示例框架是由AXI_VIP master 、slave、

passthrough组成的。左边的axi_vip_1_exdes_tb为激励文件。

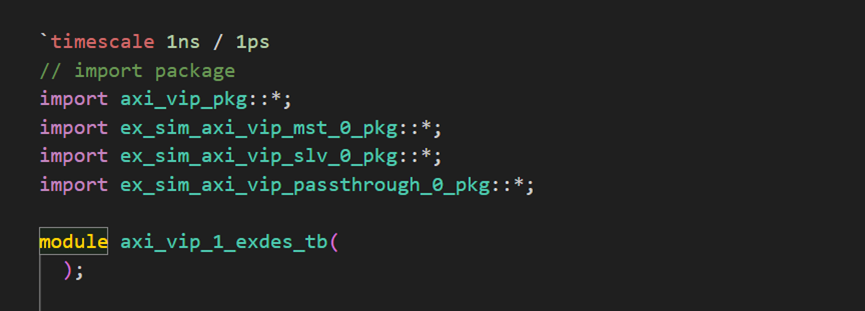

打开激励文件可以看到,在开头我们需要import一些pkg库文件

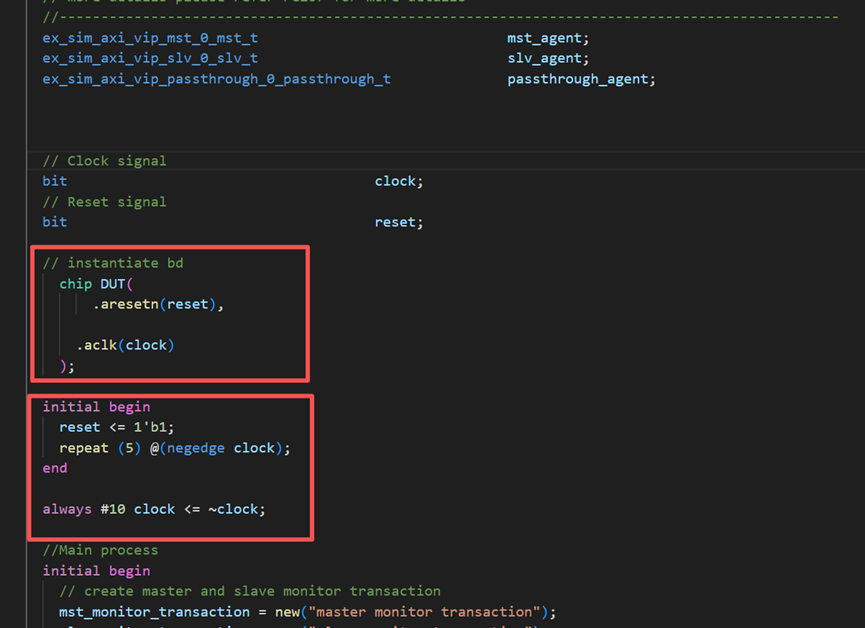

之后需要例化工程的顶层文件,需要给出准确的时钟和复位信号

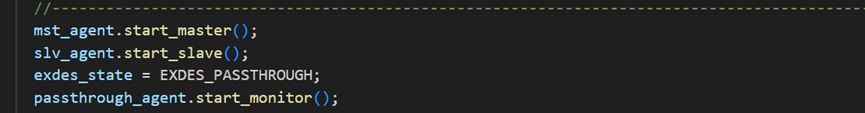

开始axi总线传输

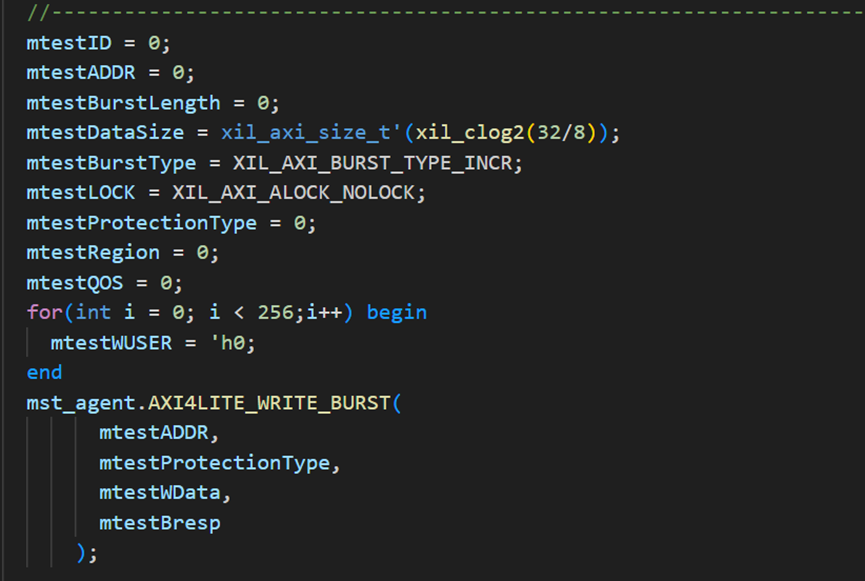

写数据

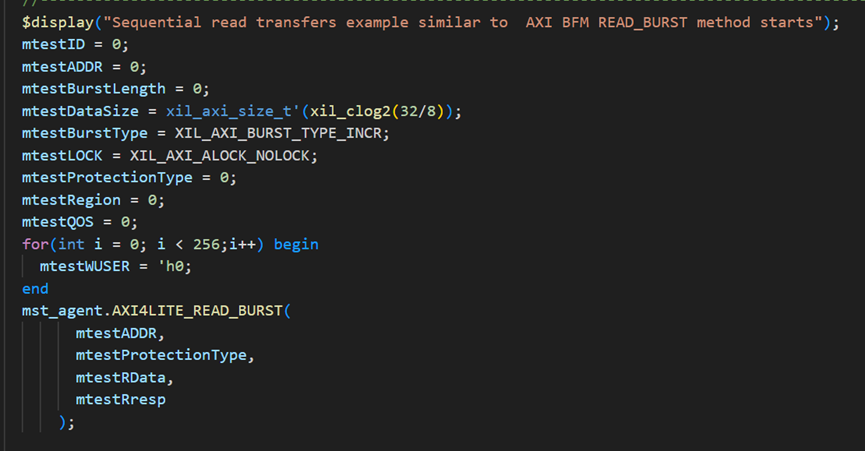

读数据

看到这里还不是很理解,没有关系,只需要记住有这么几个需要注意的关键地方即可,之后会出具体的范例加深大家的理解,大家加油哦!

总结

AXI VIP不是一个普通的IP核,它是一个完整的验证解决方案。通过熟练掌握其三种工作模式和控制方法,你可以构建出覆盖更全面、强度更高的测试环境,从而在流片前或上板前就发现那些最隐蔽、最致命的错误。

掌握AXI VIP,是你从一名FPGA代码编写者向系统级验证工程师迈进的关键一步。

在下一篇文章中,我们将加深AXI_VIP的理解,下一篇AXI VIP实战:手把手教你用AXI_VIP驱动AXI BRAM 中。我们将把本文所学的AXI VIP知识,进行一次系统的整理,欢迎大家点赞评论互动!谢谢大家

3493

3493

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?