1 配置界面说明

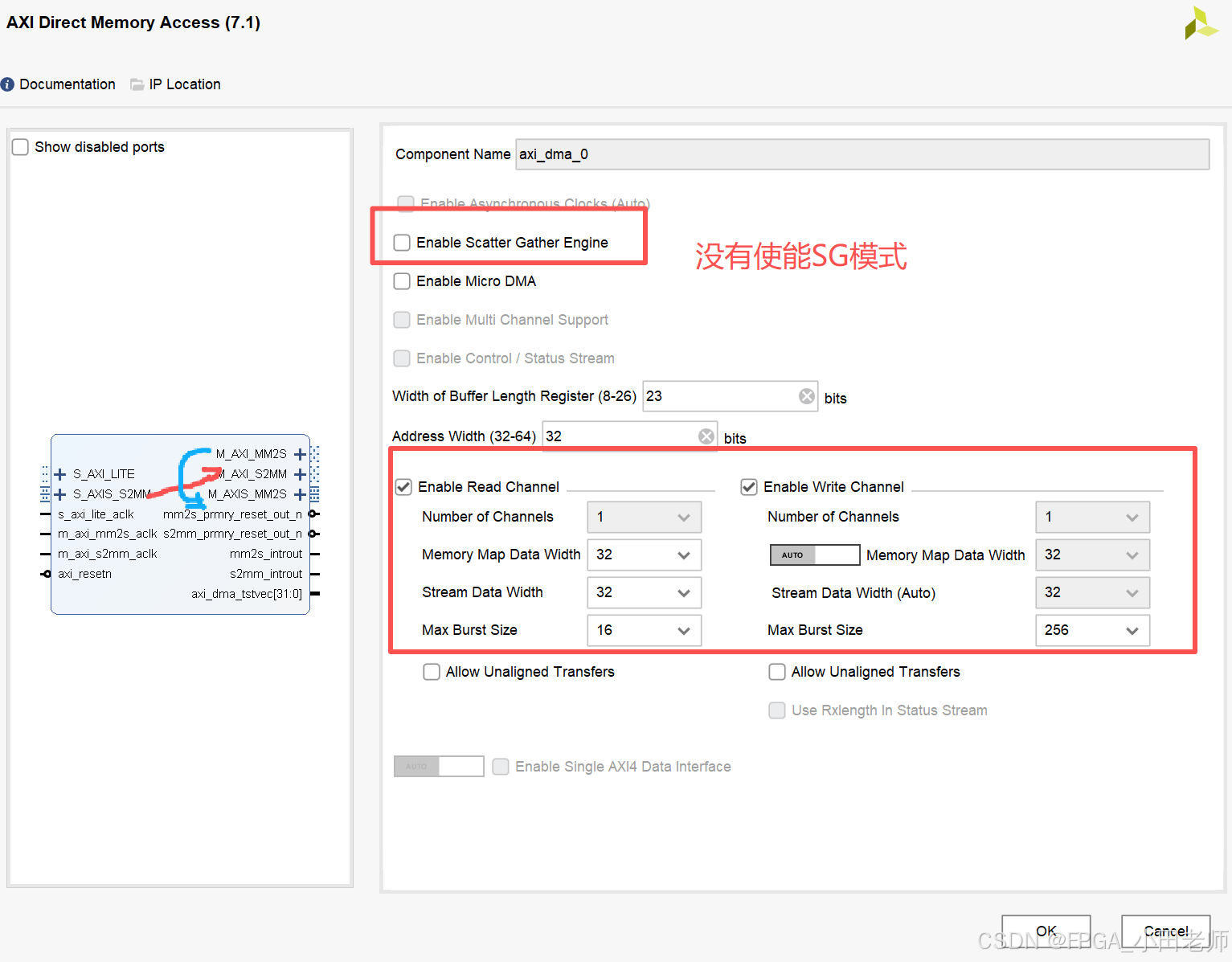

我们打开AXI Direct Memory Access 7.1的配置界面:

- 不使能SG模式--默认就是Direct Register模式

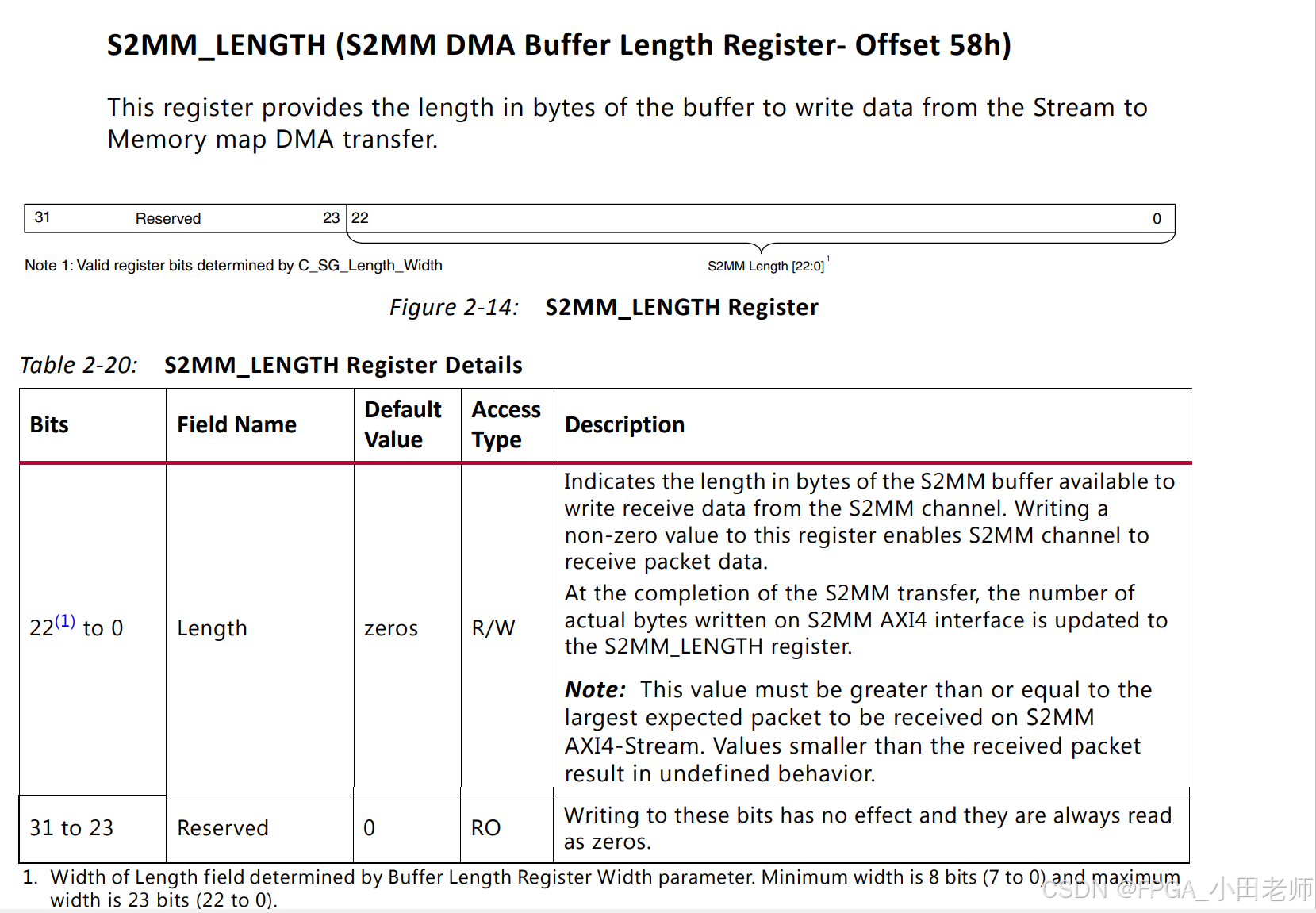

- Width of Buffer length :即buffer length对应的位宽,设置23bit,即buffer length最大设置8338607,buffer length对应的单位为Byte。

- Read Channel:M_AXI_MM2S读数据 通过 M_AXIS_MM2S发出

- Write Channel:S_AXIS_S2MM写入数据 通过 M_AXI_S2MM写给内存

所以可以理解为:Read channel对应MM2S Write channel 对应S2MM。

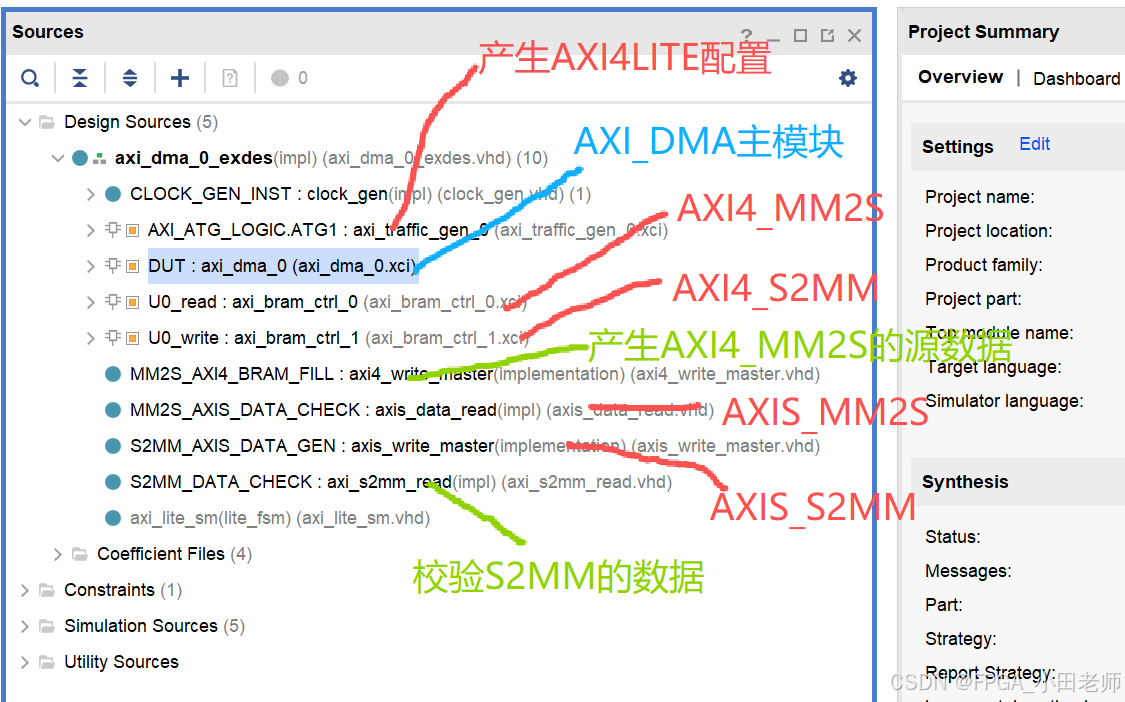

2 仿真架构说明

打开example仿真工程,可以看到架构如下

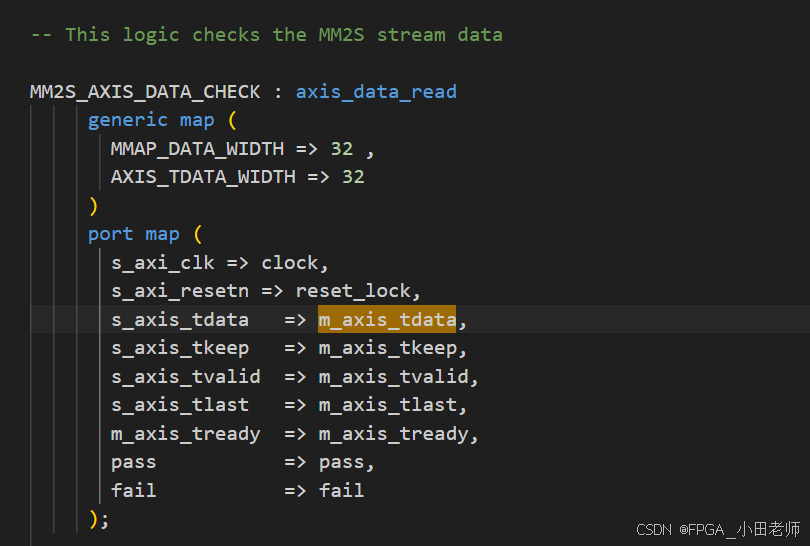

其中CHECK模块会核对读写数据的一致性,输出pass和fail信号。

3 仿真说明

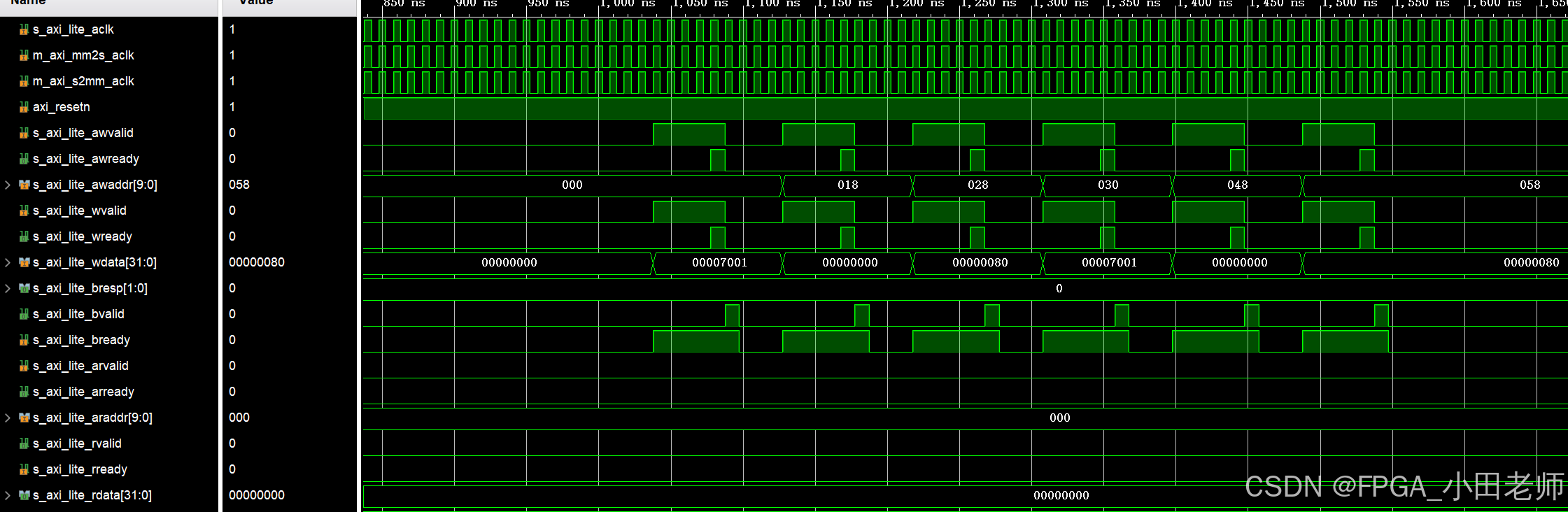

3.1 配置和寄存器详解

地址0x000 写 0x0000_7001

地址0x018 写 0x0000_0000

地址0x028 写0x0000_0080

地址0x030 写 0x0000_7001

地址0x048 写 0x0000_0000

地址0x058 写0x0000_0080

其中 0x000 0x018 0x028 对应MM2S

0x030 0x048 0x058 对应S2MM

我们只对S2MM的寄存器进行说明,S2MM与MM2S是一样的,只是寄存器地址不同

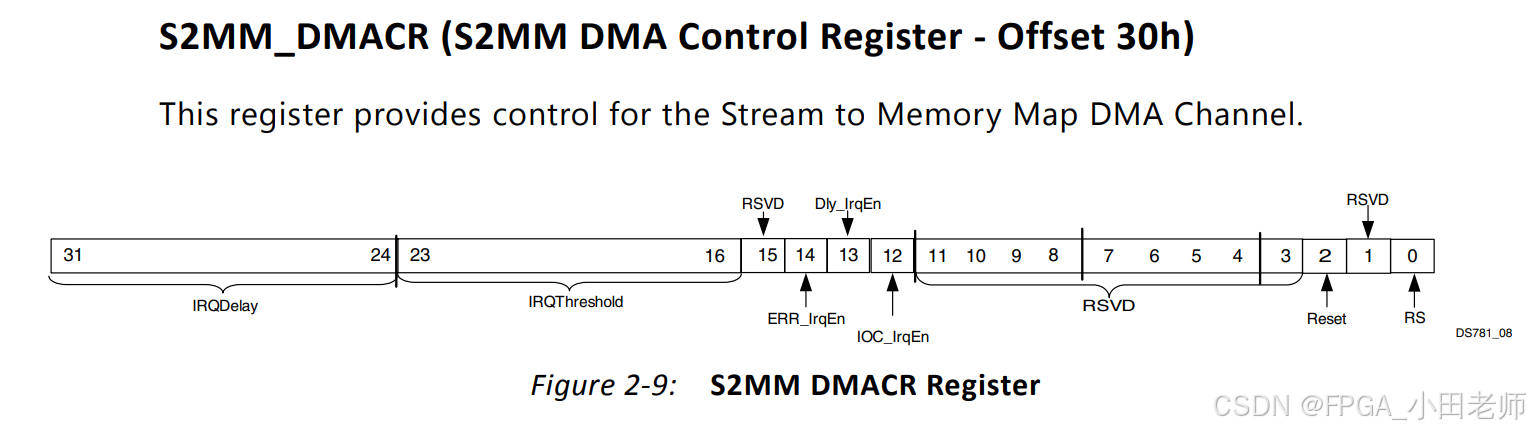

地址0x030 写 0x0000_7001

bit0=1 bit[14:12]=3'b111

bit0-->RS 0:stop 1:start

bit14:12-->使能相应的中断

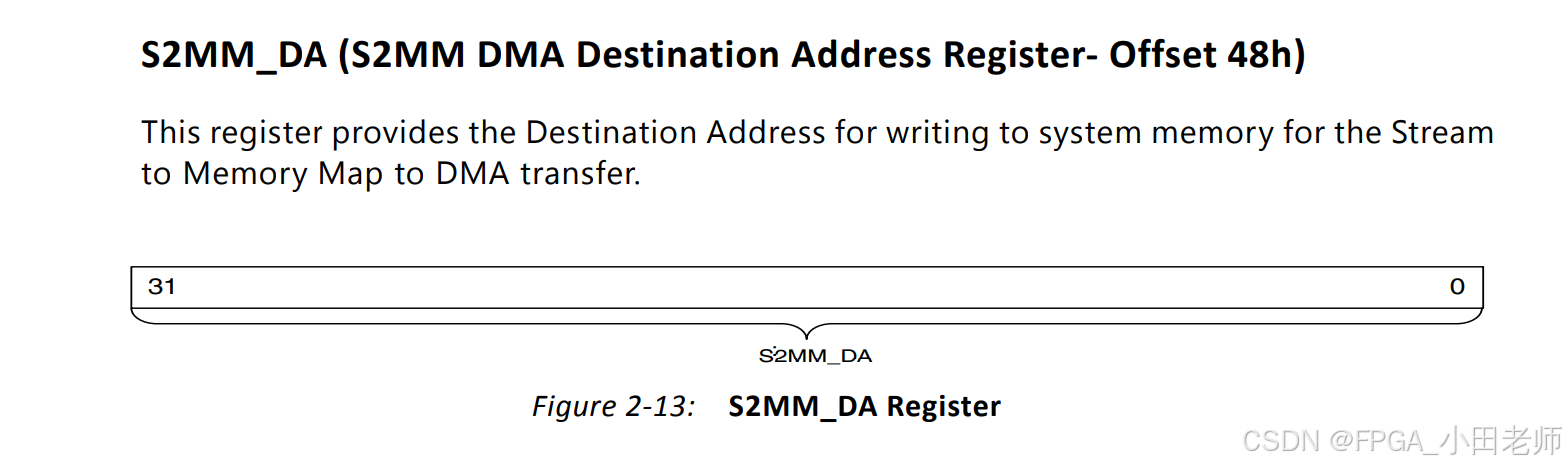

0x48--目的地址寄存器 此处是0x0000_0000

0x58--数据长度 单位Byte 此处是0x80,即一次搬移128个byte

3.2 MM2S工作流程

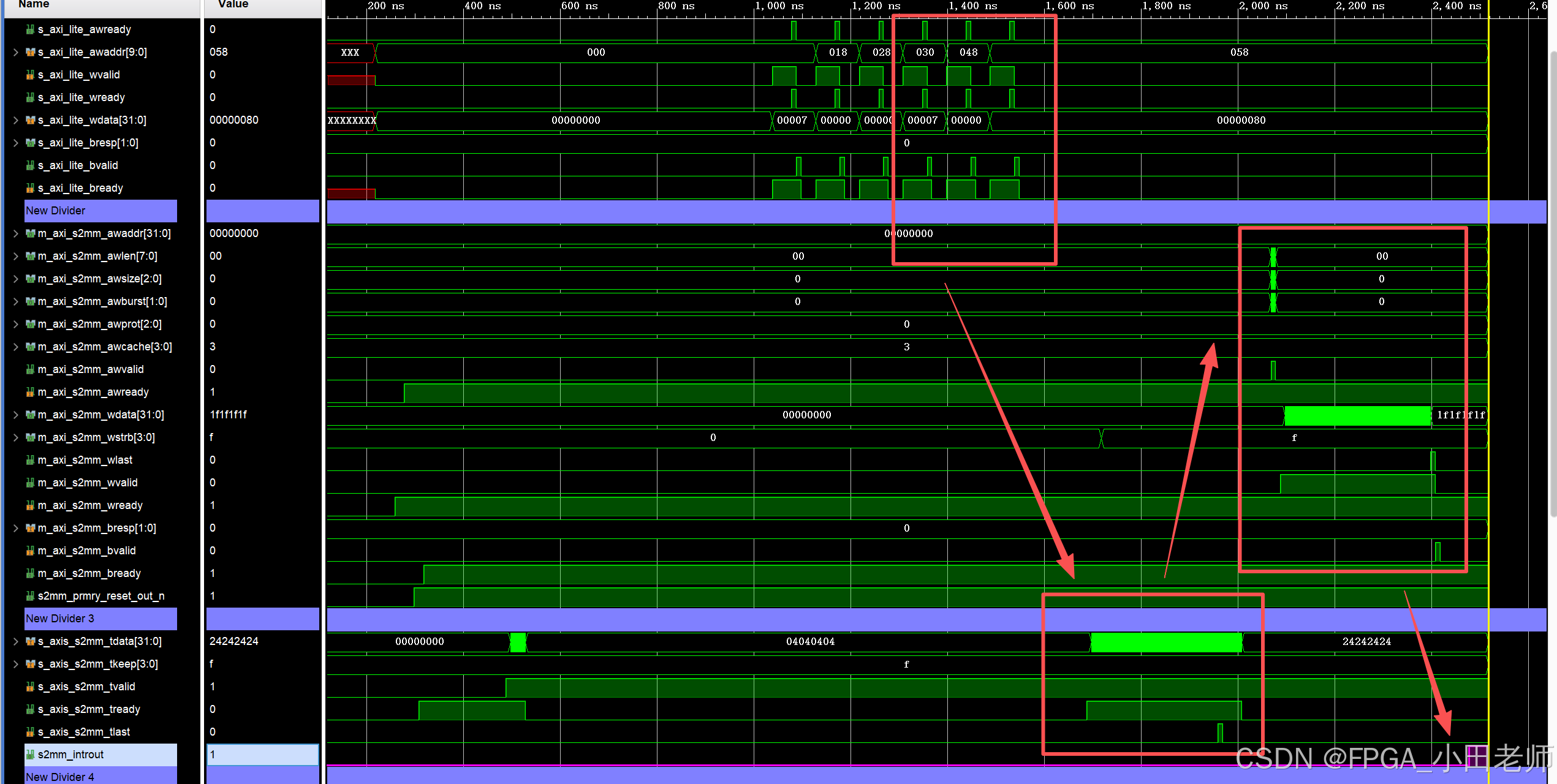

从仿真可以看出,当0x28配置完成之后,AXI4_MM2S从0x0000_0000的基地址开始取数据,并将数据转为AXIS_MM2S输出,最后一个数据的时候拉起Tlast,数据量为128个byte,传输完成之后mm2s中断拉起。

3.3 S2MM工作流程

从仿真可以看出,当0x58配置完成之后,接收AXIS_S2MM的数据,这里要注意,是接收到Tlast信号,之后,将数据通过AXI4_S2MM写入BRAM。基地址为0x0000_0000,写完之后S2MM中断拉起。

4 注意事项

- MM2S是边从内存取数据,边通过AXIS端发出,数据足够buffer length的时候,拉高tlast信号

- S2MM是先接收AXIS的数据,存在接收数据缓冲区,当接收到Tlast信号,或者数据量足够Buffer length的时候,将数据转为AXI4写入内存,也就是当数据量不足128byte,但是Tlast提前到来了,它也会执行数据搬移。

3784

3784

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?