AXI Verification IP

简介

Xilinx LogiCORE AXI Verification IP (VIP)core是为了支持客户设计的基于AXI的IP的仿真而开发的。

AXI VIP是未加密的SystemVerilog源代码,由SystemVerilog类库和可综合的RTL组成。PG267

工作模式

(VIP)核心的使用方式如下:

- 生成 master AXI命令并写入负载

- 生成 slave AXI读负载和写响应

- 检查AXI事务的协议遵从性

AXI VIP有三种配置模式:

- AXI master VIP

- AXI slave VIP

- AXI直通VIP

特点

- 支持AXI3、AXI4和AXI4- lite三个版本的AXI协议

- 可以配置为AXI主,AXI从,和直接模式

- 可以配置为模拟消息传递

- 提供仿真AXI协议检查

应用

AXI VIP是为验证和系统工程师提供的,他们需要:

- 监视两个AXI连接之间的事务

- 生成AXI事务

- 检查是否符合AXI协议

实例

https://support.xilinx.com/s/topic/0TO2E000000YNxCWAW/axi-basics-series?language=en_US&tabset-50c42=2

使用方法

tb上必须有的东西

在为AXI VIP编写tb时,必须满足以下需求。否则,AXI VIP无法工作。

- Create module test bench as all other standard SystemVerilog test benches.

module testbench();

…

endmodule - Import two required packages: axi_vip_pkg and <component_name>_pkg.

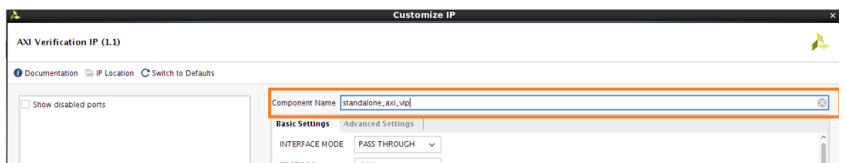

导入两个必需的包:axi_vip_pkg 和 <component_name>_pkg。 <component_name>_pkg 包括 AXI VIP 的代理类及其子类。 对于每个 VIP 实例,它都有一个组件包,该组件包在创建输出时自动生成。 该组件包包括一个参数化 agent 的 typedef 类。 Xilinx 建议导入此包,因为重新配置 VIP 对测试台没有影响。 图 6-5 显示了如何从独立 AXI VIP 中检索 <component_name>_pkg。

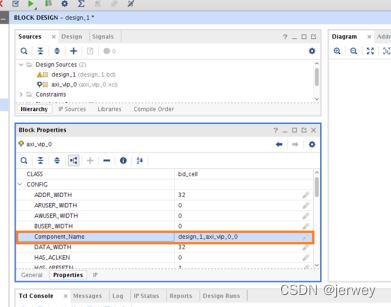

图 6-6 显示了如何从 IP 集成器设计中获得 <component_name>_pkg。 首先,选择 VIP,然后在 Block Properties 窗口中单击 Properties。 然后,在 CONFIG 列下选择 Component_Name

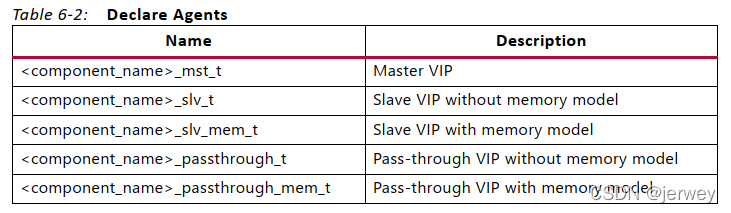

- 声明代理。 必须为一名 AXI VIP 声明一名代理。 根据 AXI VIP 接口模式,应该调用不同的 typedef 类来声明代理。

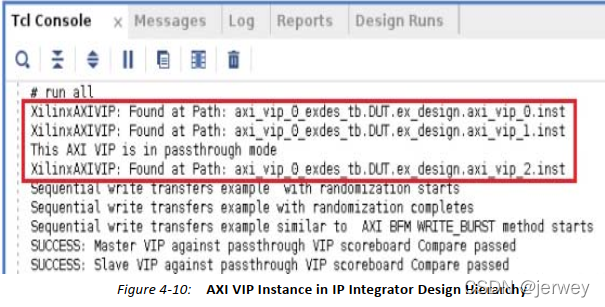

- 为代理创建一个新函数,并将IF的层次结构路径正确地传递到新函数中。在将代理设置为new之前,使用空的测试工作台运行模拟,以找到AXI VIP实例的层次结构路径。这样的消息将显示出来,然后将路径放入一个新函数中(如图4-10所示)

agent = new(“my VIP agent”, <hierarchy_path>.IF);

//Import two required packages: axi_vip_pkg and <component_name>_pkg.

import axi_vip_pkg::*;

import design_1_axi_vip_0_0_pkg::*;

module AXI_tb();

// Declare the agent

design_1_axi_vip_0_0_slv_mem_t slv_agent;

initial begin

//Create an agent

slv_agent = new("master vip agent",UUT.design_1_i.axi_vip_0.inst.IF);

// set print out verbosity level

slv_agent.set_verbosity(400);

//Start the agent

slv_agent.start_slave();

end

启动代理

为了让VIP开始运行,必须调用启动代理。下面展示了主、从和直通vip如何开始运行

AXI Master VIP

Start agent:

mst_agent.start_master();

Then, generate the transaction. For more information about how to generate transaction,

see the Vivado example design simset and look for mst_stimulus.sv.

AXI Slave VIP

Start agent:

slv_agent.start_slave();

如果使用 <component_name>_slv_mem_t,则在代理中处理写入响应和读取响应。 用户环境在这里不需要做任何事情。 有关更多信息,请参阅 Vivado 示例设计 simset 并查找 mem_basic_stimulus.sv/mem_stimulus.sv

如果使用 <component_name>_slv_t,如果 READ_WRITE_MODE 不是 READ_ONLY,则用户环境必须填写写入响应,如果 READ_WRITE_MODE 不是 WRITE_ONLY,则必须填写读取响应。 有关更多信息,请参阅 Vivado 示例设计 simset 并查找 slv_basic_stimulus.sv/slv_stimulus.sv。

AXI Pass-Through VIP

Runtime Slave Mode

Runtime Mater Mode

Runtime Pass-Through Mode

Other

AXI Protocol Checker core 监控AXI接口。当连接到接口时,它会主动检查协议违反,并提供发生违反的指示。这些检查是ARM在AMBA 4、AXI4、AXI4- lite和AXI4- stream协议断言用户指南中提供的System Verilog协议断言的综合版本 (PG101)

pg267

Xilinx LogiCORE AXI Verification IP (VIP) 是为了支持基于AXI的IP仿真,提供AXI3、AXI4和AXI4-lite协议的支持。VIP有三种模式:主、从和直通,适用于验证和系统工程师进行事务监视、生成和协议检查。使用时,需在tb中创建代理,启动相应模式的VIP,如mst_agent.start_master()或slv_agent.start_slave()。

Xilinx LogiCORE AXI Verification IP (VIP) 是为了支持基于AXI的IP仿真,提供AXI3、AXI4和AXI4-lite协议的支持。VIP有三种模式:主、从和直通,适用于验证和系统工程师进行事务监视、生成和协议检查。使用时,需在tb中创建代理,启动相应模式的VIP,如mst_agent.start_master()或slv_agent.start_slave()。

1347

1347

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?