《FPGA DDR3权威指南》系列导航

《FPGA DDR3权威指南》系列旨在从零到一带你彻底掌握DDR3设计精髓,关注我,你可以:

- 系统学习,避免知识碎片化。

- 获得更新提醒,不错过任何一篇干货

本篇是该系列的第三篇内容

上一篇:FPGA DDR3实战(二):手把手教你仿真DDR3(MIG IP核)_fpga怎么模拟ddr3-优快云博客

下一篇:FPGA DDR3实战(四):DDR地址映射自动化测试(1)—— 测试程序设计与代码逻辑-优快云博客

一 引言

在之前的文章中,我们分别完成了两件重要的工作:

第一:我们深入剖析了MIG IP核(AXI4接口)的核心信号,并利用简单的Example Design验证了IP核本身与DDR3模型的基本功能。

第二:我们系统学习了AXI Verification IP (VIP),并通过驱动简单的AXI BRAM,熟悉了其作为主设备的工作模式和控制方法。

然而,一个关键的挑战摆在我们面前:Example Design中的流量发生器(Traffic Generator)是一个“黑盒”,我们难以定制其行为来模拟真实的用户逻辑。 当我们需要测试特定场景、注入异常或进行压力测试时,它就显得力不从心。

本篇的核心价值,就在于解决这个问题。

我们将:

-

摒弃“黑盒”Traffic Generator,使用灵活、可编程的AXI VIP来替代它。

-

通过编写精细的测试脚本,实现可控、可观测、可复现的DDR3读写测试。

-

构建一个完全由我们掌控的、工程级的DDR3仿真验证环境。

二 实战平台搭建

接下来我们搭建一下AXI_VIP+DDR3的工程,来带大家进行DDR3的工程级仿真。

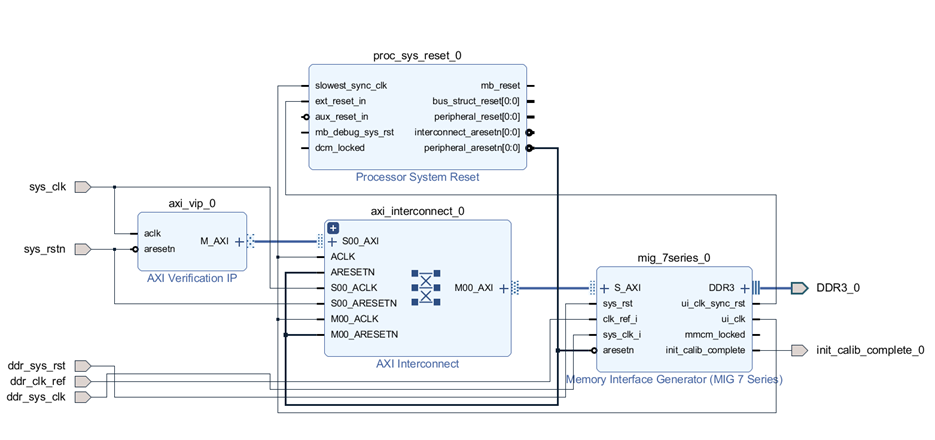

搭建的环境如下

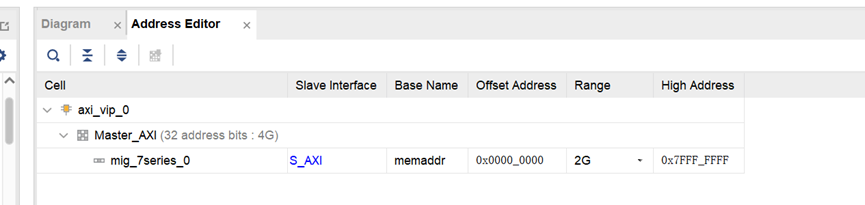

地址分配如下

点击 Validate Design 对blockDesign进行编译

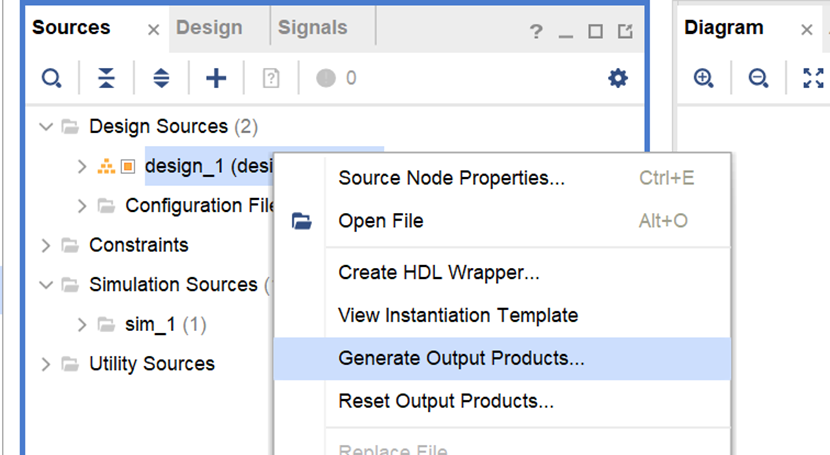

右键选择Generate Output Products 对Block Design中的所有ip核进行编译

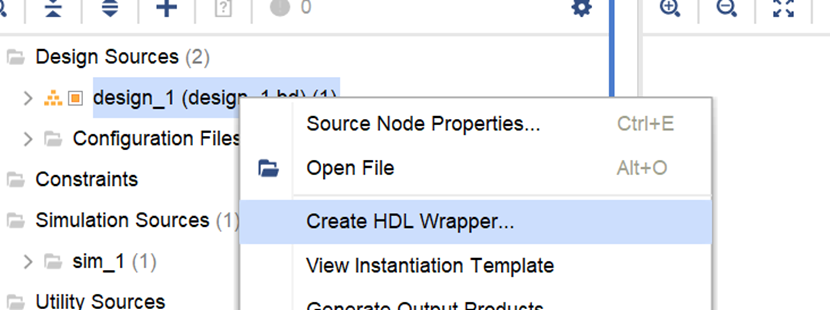

编译完成之后,右击选择Create HDL Wrapper 生成之后用于例化的顶层文件。

三 编写测试激励

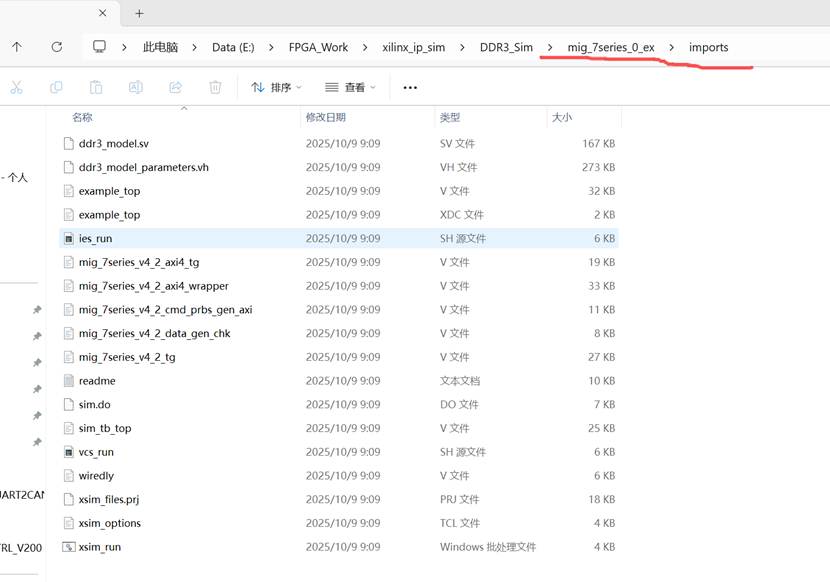

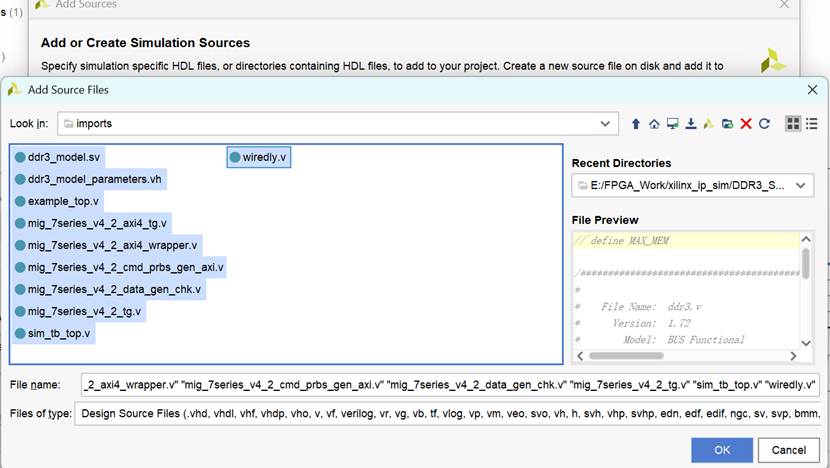

1 将xilinx自带的mig的example工程中的import内部的文件导入到现在的工程里面(mig的example的生成参考:FPGA DDR3实战(二):手把手教你仿真DDR3(MIG IP核))。

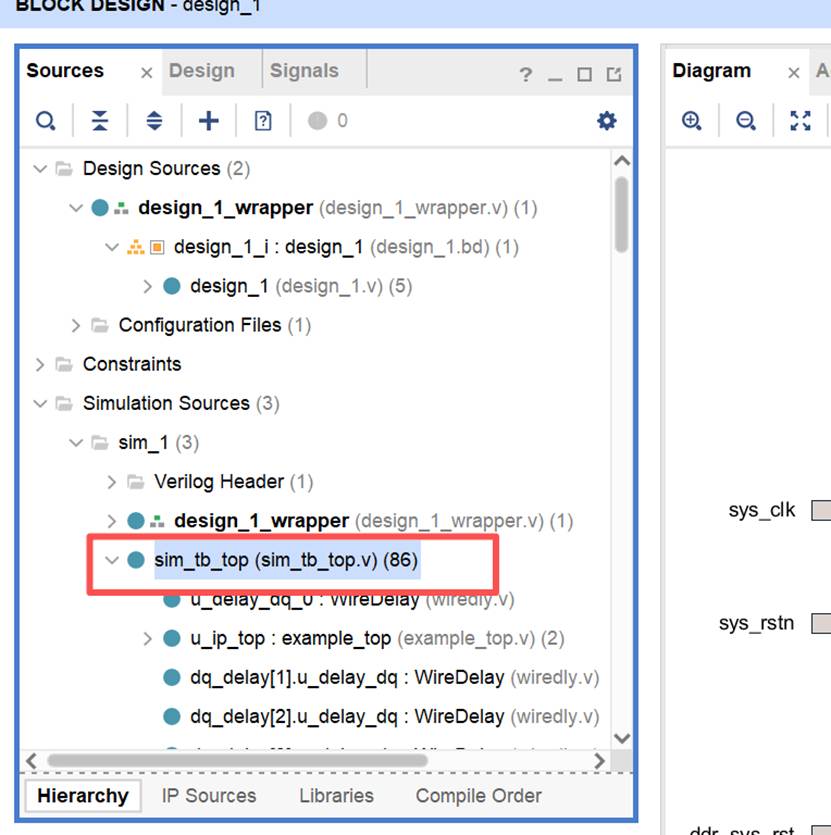

2 导入之后在Sim Source里面就能看到sim_tb_top,我们将在这个文件上进行修改

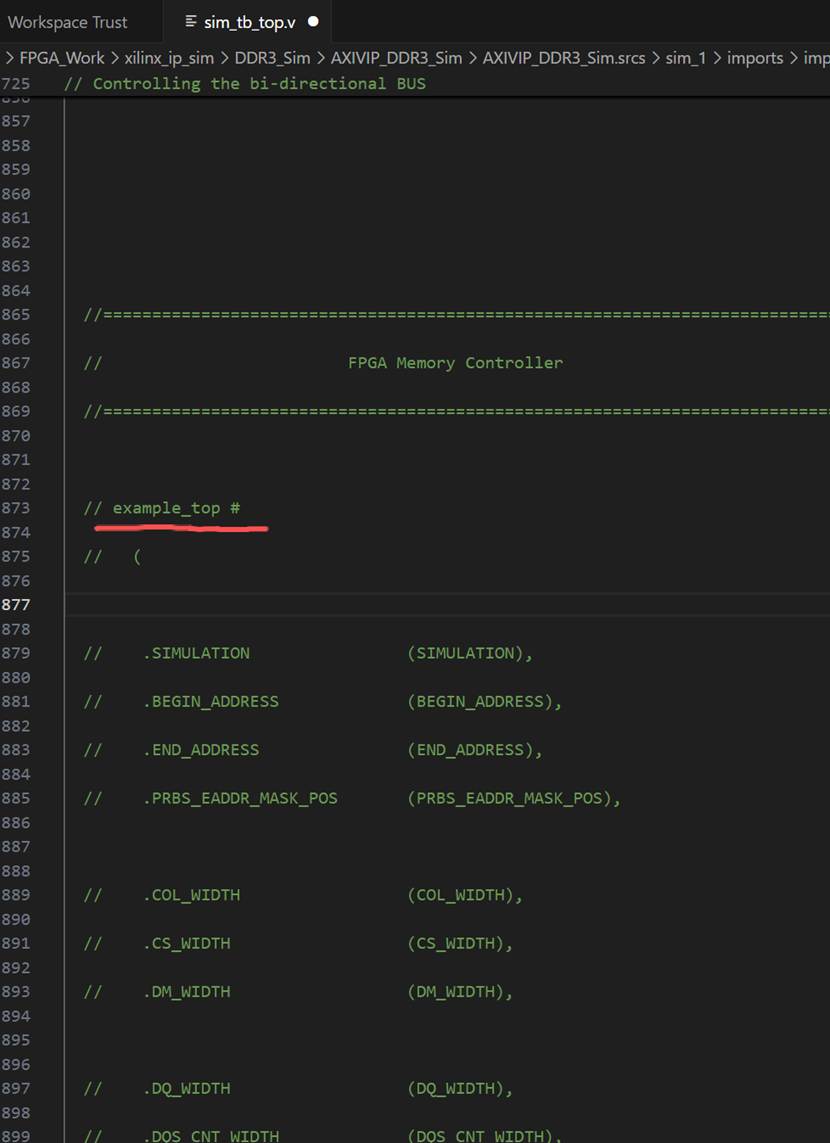

3 将文件中例化的example_top模块注释掉

4 例化我们刚才生成的那个wrapper文件

接下来,开始添加激励信号,参考FPGA验证利器:全方位解析AXI Verification IP (AXI VIP) 或者 AXI VIP实战:手把手教你用AXI_VIP驱动AXI BRAM。

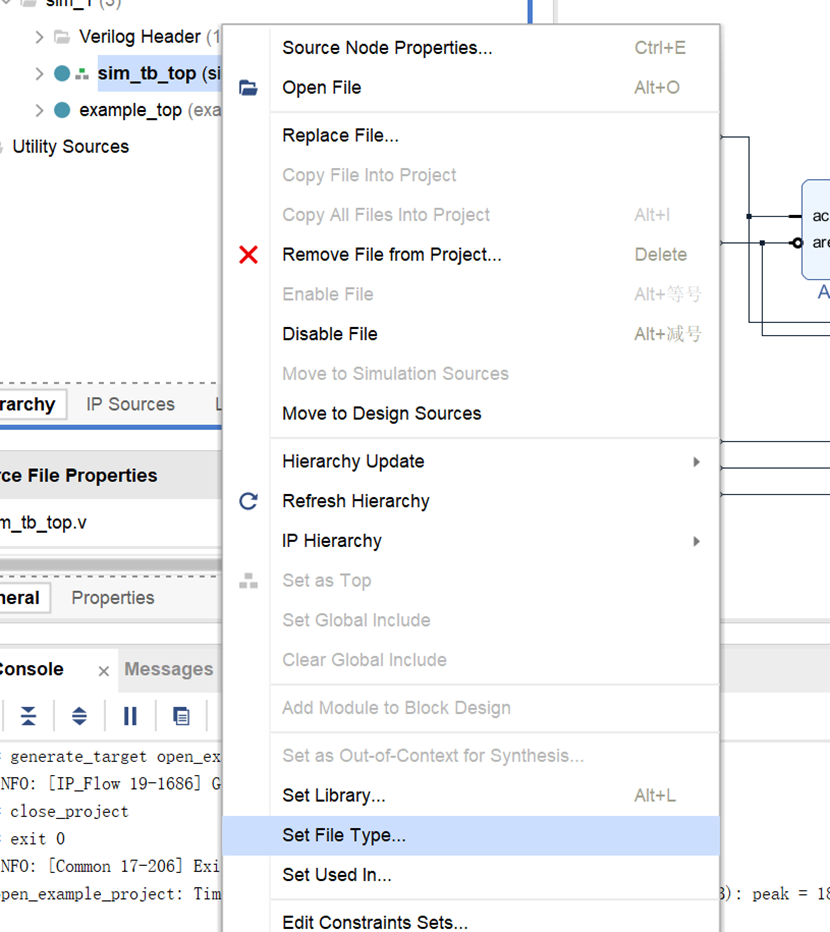

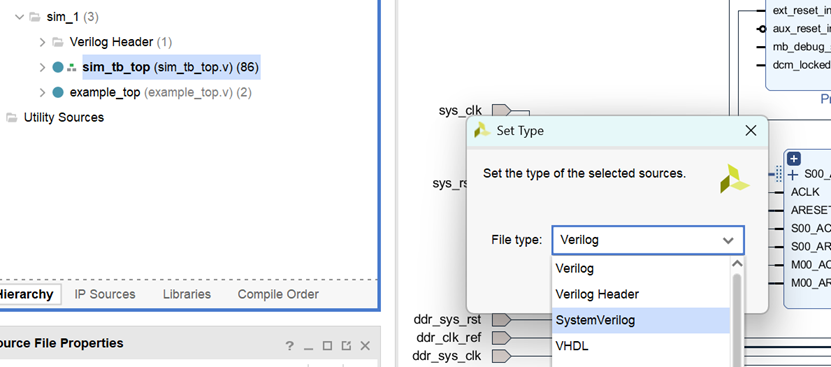

5 将sim_tb_top设置为system Verilog

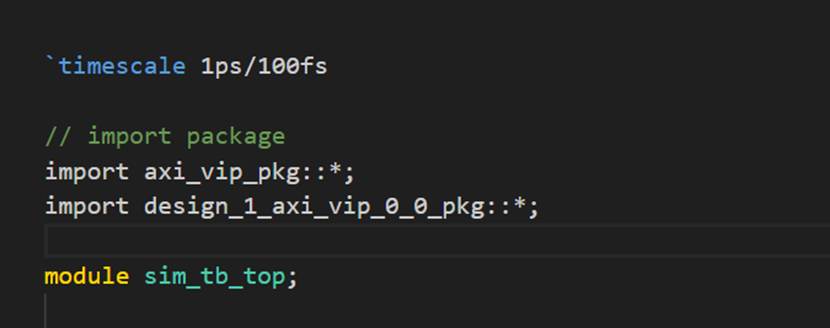

6 导入pkg

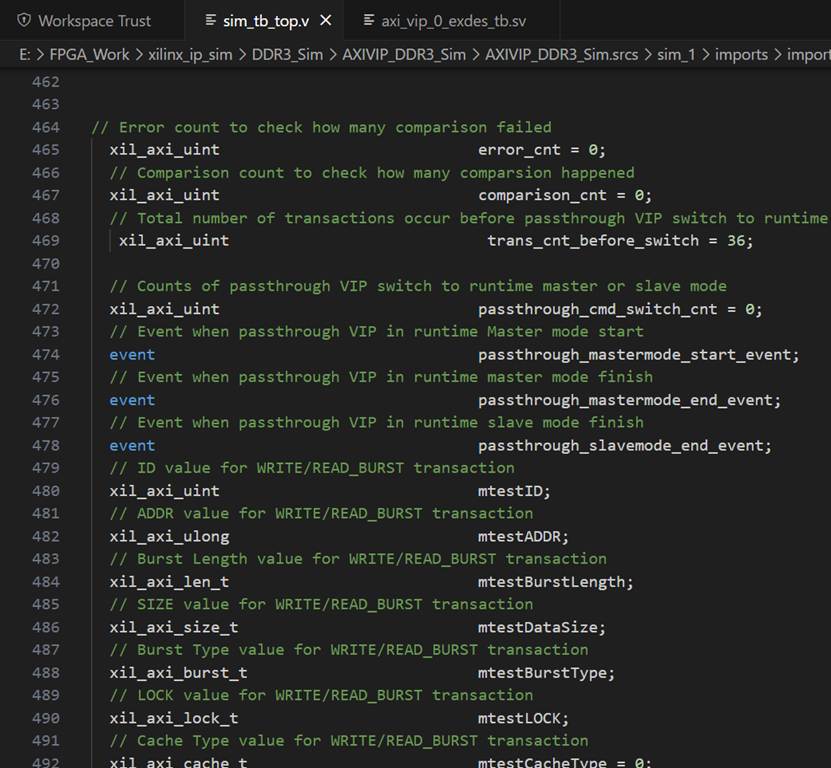

7 添加axivip相关的变量声明

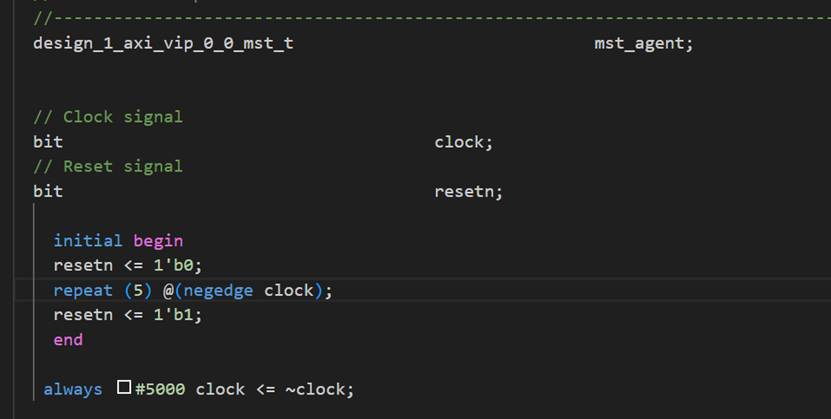

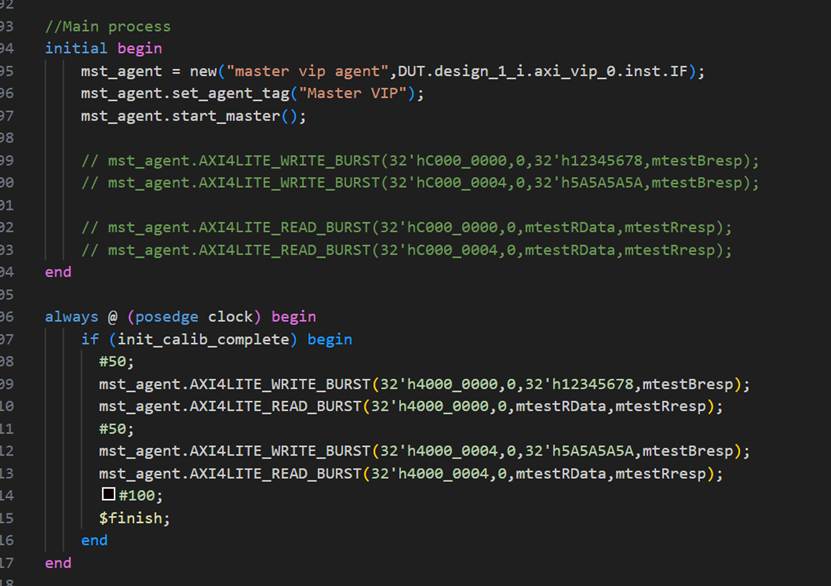

8 系统时钟和复位信号生成

9 添加测试激励,注意必须是DDR3初始化完成之后再进行数据读写,DDR3初始化完成的标志为init_calib_complete拉高。

四 DDR3仿真

文件修改完成之后,我们点击Run Simulation进行仿真,这里仿真很慢,大家一定耐心等待。

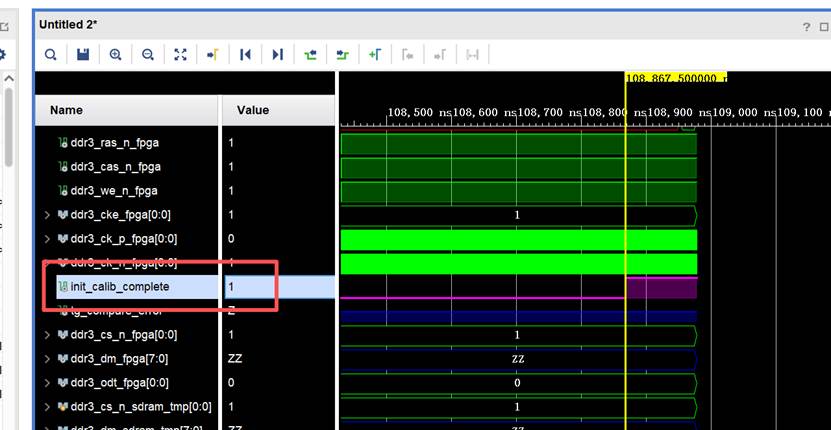

大约在108us的时候,init_calib_complete拉起,既DDR3初始化完成。

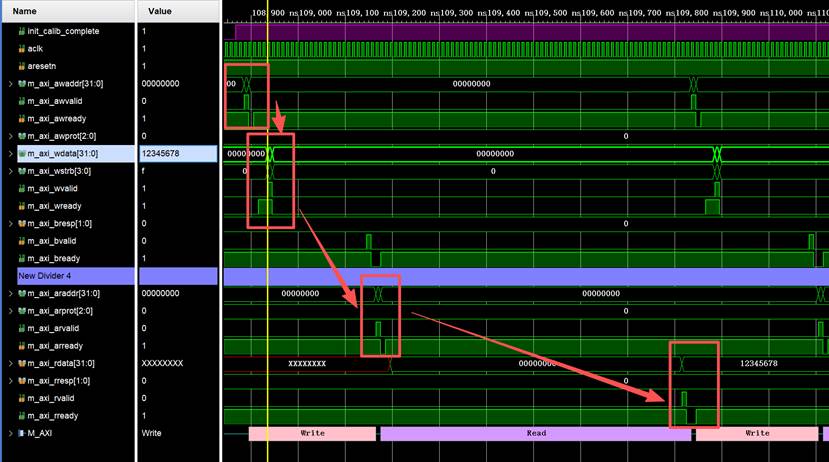

之后我们查看AXI总线,可以看出我们第一笔往0x4000_0000地址写了0x12345678

之后又从0x4000_0000读出数据,读出数据结果为0x12345678,读写数据一致。

说明此次DDR3仿真结果正常。

总结

至此,我们成功地完成了一次从“组件认知”到“系统验证”的跨越。本文作为DDR3系列的核心实战篇,我们不再依赖于MIG Example Design中固定的流量生成器,而是手握AXI VIP这一利器,构建了一个完全自主可控的DDR3仿真验证环境。

掌握“AXI VIP + DDR3”的仿真,意味着你不仅学会了如何使用一个工具,更重要的是掌握了验证复杂AXI总线系统的标准方法。 这套方法可以无缝迁移到你对PCIe、以太网等其它高速AXI接口的验证工作中,其价值远超本篇内容本身。

下一篇,我们进行 FPGA工程实战:DDR地址映射自动化测试(1)—— 测试程序设计与代码逻辑 的介绍,通过这一篇,大家能够了解到一种高效的DDR自动化测试方案,大家多多点赞关注,欢迎大家互动留言!!!

1264

1264

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?