1 引言

在嵌入式系统设计中,I2C(Inter-Integrated Circuit)总线因其简单的两线设计和灵活的多设备支持,成为最常用的串行通信协议之一。本文将深入解析I2C协议的各个方面,为后续的FPGA实现和调试实践打下坚实基础。

2 I2C协议基础概览

2.1 什么是I2C?

I2C是由飞利浦半导体(现NXP半导体)在1980年代开发的一种同步、半双工、多主从的串行通信总线。其核心特点是:

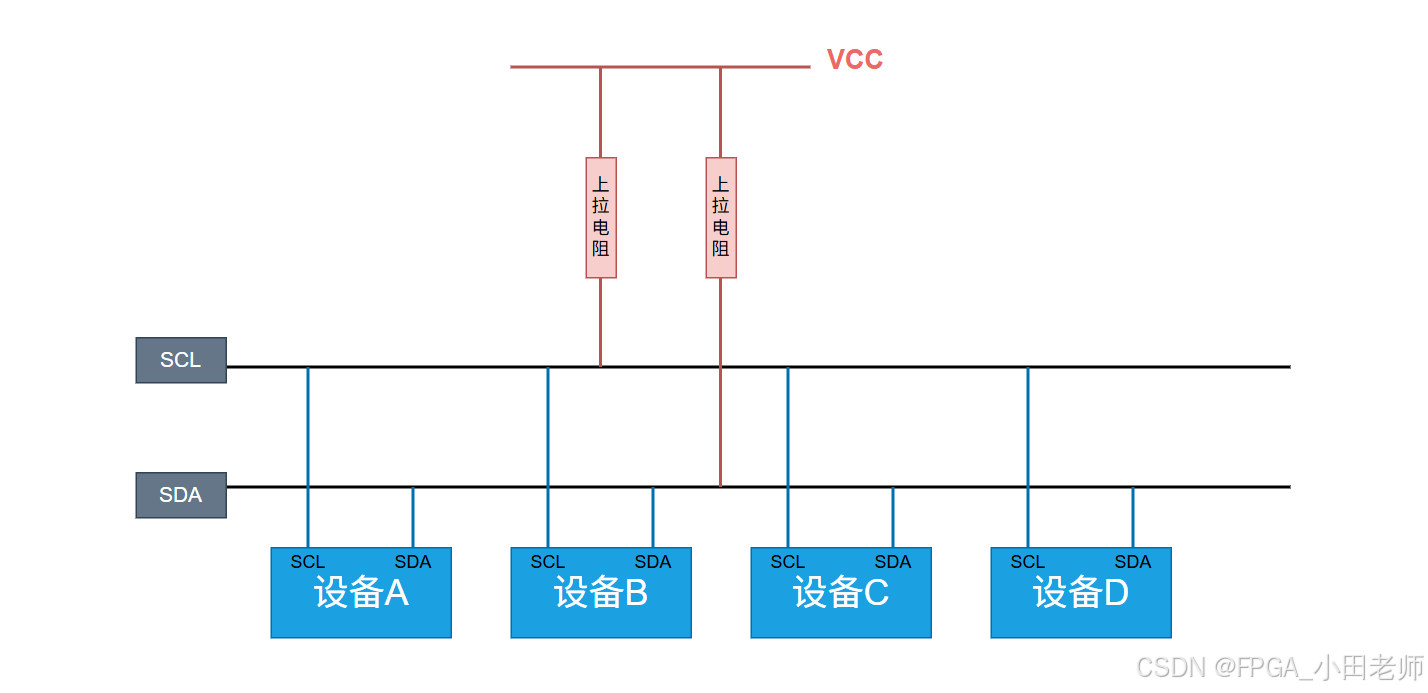

-

仅需两根信号线:SDA(串行数据线)和SCL(串行时钟线)

-

支持多主多从:多个主设备可以共享同一总线

-

软件地址寻址:通过地址识别不同从设备

2.2 物理层特性

3 I2C通信时序详解

3.1 基本时序单元

起始条件(START)

// 时序要求:SCL为高时,SDA从高变低

// 代码表示:

scl = 1'b1;

sda = 1'b1; // 初始状态

#(setup_time);

sda = 1'b0; // 起始条件

#(hold_time);

scl = 1'b0; // 准备数据传输停止条件(STOP)

// 时序要求:SCL为高时,SDA从低变高

scl = 1'b0;

sda = 1'b0; // 确保SDA在SCL变高前稳定

#(setup_time);

scl = 1'b1;

#(setup_time);

sda = 1'b1; // 停止条件重复起始条件(Repeated START)

用于在不释放总线的情况下开始新的传输,提高了总线利用率。

3.2 起始和停止时序

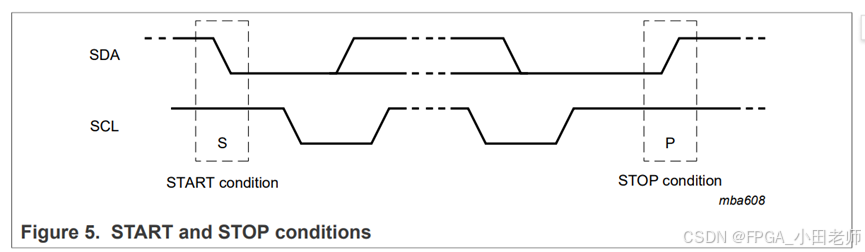

所有传输都以起始信号(S)开始,并以停止信号(P)结束(见图 5)。当串行时钟线(SCL)为高电平时,串行数据线(SDA)上由高到低的跳变定义为起始条件。当 SCL 为高电平时,SDA 上由低到高的跳变定义为停止条件。

起始(START)和停止(STOP)条件始终由控制器生成。在起始条件之后,总线被视为处于忙状态。在停止条件之后的某一特定时间,总线再次被视为空闲。这种总线空闲状态在第6节中有具体说明。

如果产生的是重复起始(Sr)条件而非停止条件,则总线保持忙状态。在这方面,起始(S)和重复起始(Sr)条件在功能上是相同的。

3.3 数据传输时序

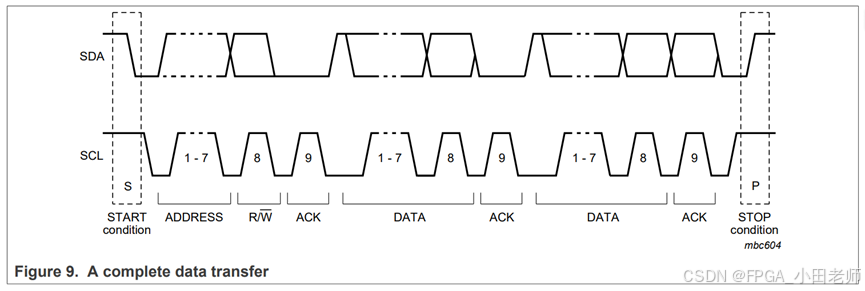

I2C总线的数据传输遵循严格的格式规范,所有通信都由起始条件(S)开始,由停止条件(P)结束。数据传输的基本流程如下:

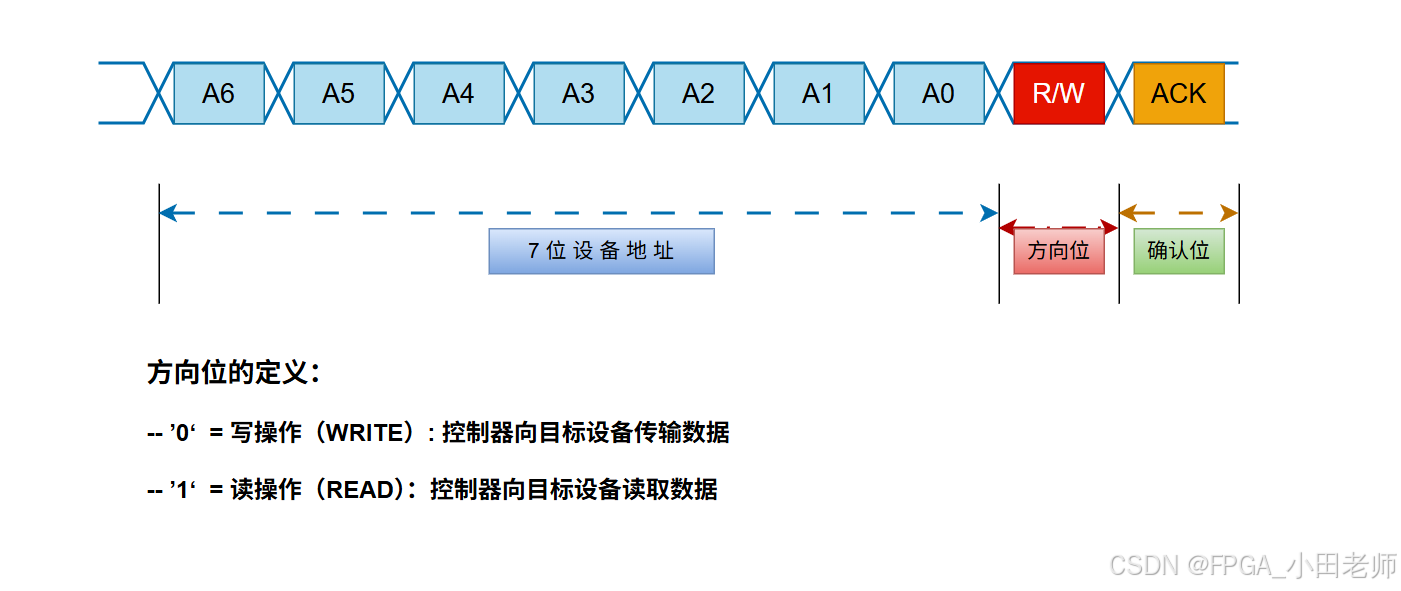

起始条件(S) → 目标地址(7位) → 方向位(R/W) → 确认位(ACK) → 数据字节 → 确认位 → ... → 停止条件(P)

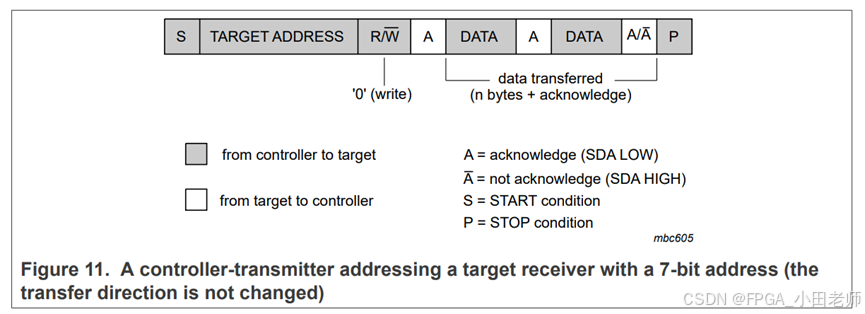

4 三种基本传输模式

4.1 模式一:控制器写操作

控制器-发送器 → 目标-接收器

-

特点:传输方向保持不变

-

确认机制:每个数据字节后由目标设备产生ACK

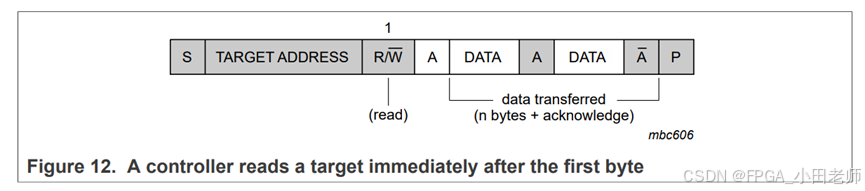

4.2 模式二:控制器读操作

控制器-接收器 ← 目标-发送器

-

角色转换:第一个ACK后,控制器变为接收器,目标变为发送器

-

确认机制:

-

第一个ACK由目标设备产生

-

后续ACK由控制器产生

-

最后一个字节后控制器发送NACK,然后产生停止条件

-

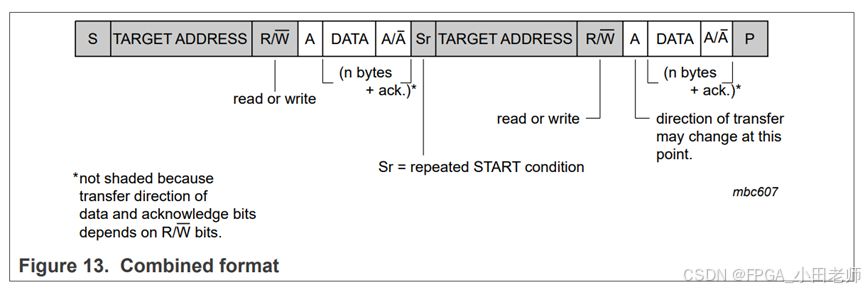

4.3 模式三:组合传输模式

混合读写操作

-

特点:通过重复起始条件(Sr)改变传输方向

-

方向反转:重复起始条件后,R/W位反转

-

应用场景:常用于串行存储器操作

4.4 关键技术要点

重复起始条件(Sr)的优势

-

保持总线控制:无需释放总线即可开始新的传输

-

提高效率:减少总线占用时间

-

原子操作:确保相关操作的完整性

确认机制规则

-

每个字节后必须跟随确认位

-

ACK(确认) = 低电平(0)

-

NACK(非确认) = 高电平(1)

-

最后一个读取字节:控制器必须发送NACK

4.5 特殊情况和注意事项

非法格式处理

-

空消息:起始条件后立即跟随停止条件属于非法格式

-

设备兼容性:多数现代设备能够正确处理这种异常情况

设备地址管理

-

唯一地址:每个设备必须有唯一的7位地址

-

组播支持:多个相同地址设备可同时响应(需特殊设计)

-

总线切换器:使用如PCA9546A等设备实现多设备管理

总线逻辑复位

所有I2C兼容设备在检测到起始条件或重复起始条件时,必须:

-

重置总线逻辑

-

准备接收目标地址

-

即使格式不正确也要响应

4.6 实际应用示例:串行存储器访问

// 典型的串行存储器读写序列

// 1. 写入存储器地址

START + 设备地址(写) + ACK + 存储器地址 + ACK

// 2. 重复起始条件改变方向

Sr + 设备地址(读) + ACK

// 3. 读取数据

数据字节1 + ACK + 数据字节2 + ACK + ... + 数据字节N + NACK + STOP5 I2C数据帧结构

5.1 完整的通信帧

[START] + [7位地址] + [R/W位] + [ACK] + [8位数据] + [ACK] + ... + [STOP]

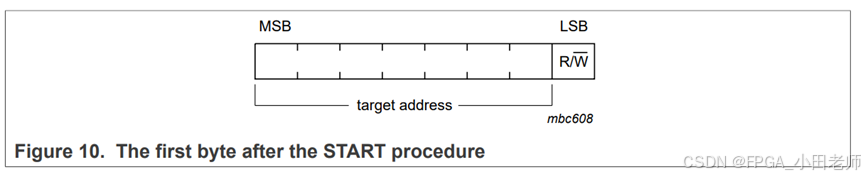

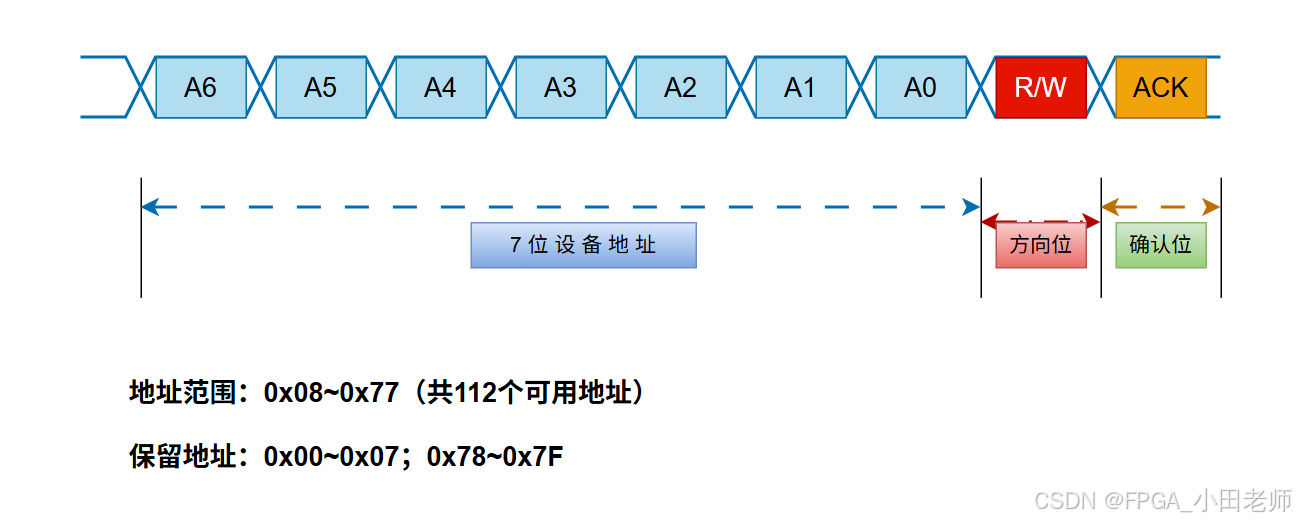

5.2 地址帧格式

5.2.1 7位地址模式

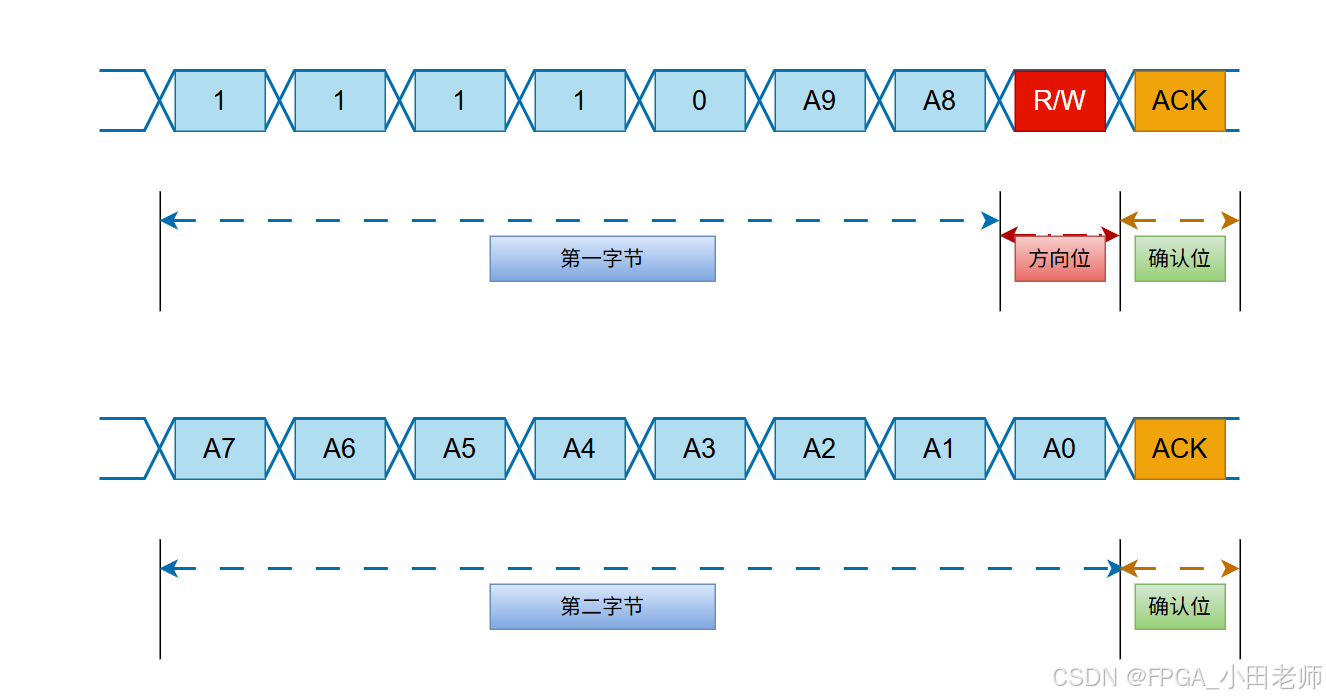

5.2.2 10位地址模式

10位寻址是I2C总线协议的重要扩展,它显著增加了可用的设备地址数量。这种寻址模式与传统的7位寻址完全兼容,可以在同一总线上混合使用,并支持所有速度模式,尽管目前在业界尚未得到广泛应用。

地址格式组成

10位地址由起始条件后的两个连续字节构成:

地址空间分配

-

可用地址:4 × 256 = 1024个地址

-

保留空间:前缀

11111XXX保留给未来扩展使用 -

实际使用:前缀

11110XX用于10位寻址

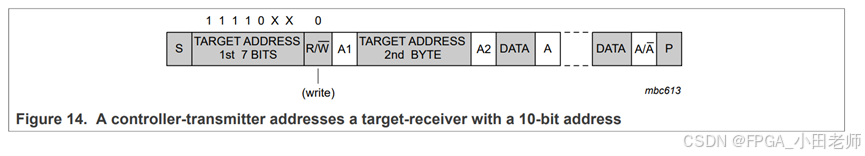

10位寻址通信流程

控制器写操作(10位地址)

匹配过程:

-

所有10位设备比较第一字节的前7位(

11110+A9+A8) -

匹配设备检查R/W位是否为0(写操作)

-

多个设备可能产生A1应答

-

匹配设备比较第二字节的完整8位地址

-

唯一匹配的设备产生A2应答,进入被寻址状态

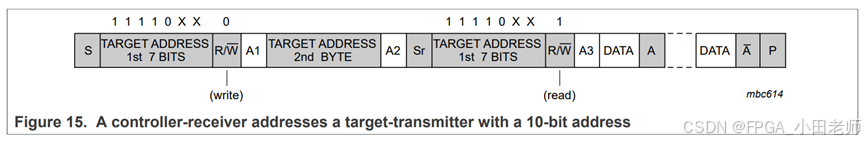

控制器读操作(10位地址)

关键特性:

-

需要重复起始条件(Sr)来改变传输方向

-

第二次地址发送时R/W位变为1(读操作)

-

匹配设备会"记住"之前的寻址,只比较地址前缀

5.3 特殊功能处理

广播呼叫支持

10位寻址设备对广播呼叫(地址0x00)的响应方式与7位设备完全相同。在广播呼叫后,控制器可以发送其10位地址,格式为:

广播呼叫地址(0x00) + ACK + 地址低8位 + ACK + 地址高2位 + ACK

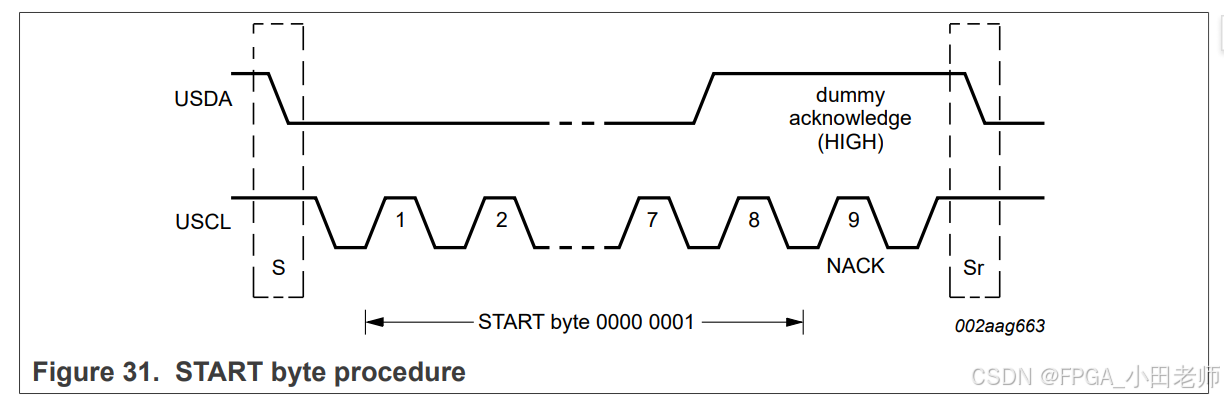

起始字节功能

起始字节00000001(0x01)可以像7位寻址那样用于10位寻址之前,为低速微控制器提供额外的准备时间。

状态保持机制

被成功寻址的10位设备将保持被寻址状态,直到:

-

接收到停止条件(P)

-

接收到重复起始条件(Sr)后跟不同的目标地址

6 I2C传输模式与速度等级

标准模式(Standard-mode)

-

速度:最高100 kbit/s

-

特性:基础通信,兼容性最好

快速模式(Fast-mode)

-

速度:最高400 kbit/s

-

新增特性:

-

更严格的时序要求

-

输入滤波减少噪声敏感度

-

更快的上升时间

-

快速模式+(Fast-mode Plus)

-

速度:最高1 Mbit/s

-

特性:更高的驱动能力要求

高速模式(High-speed mode)

-

速度:最高3.4 Mbit/s

-

特殊机制:

-

需要主设备在传输开始后切换到高速模式

-

使用电流源上拉代替电阻上拉

-

7 电气特性与信号完整性

7.1 开漏输出特性

// I2C设备只能驱动低电平,无法驱动高电平

assign sda = (sda_oe) ? 1'b0 : 1'bz;

assign scl = (scl_oe) ? 1'b0 : 1'bz;

// 高电平由上拉电阻提供

// VCC ---- RP ---- SDA/SCL7.2 典型电阻值选择

| 模式 | 总线电容 | 推荐电阻 | 备注 |

|---|---|---|---|

| 标准模式 | <100pF | 10kΩ | 低功耗 |

| 标准模式 | 100-200pF | 4.7kΩ | 通用 |

| 快速模式 | 100-200pF | 2.2kΩ | 高速 |

| 高速模式 | <100pF | 电流源 | 特殊设计 |

8 官方协议文档获取

-

搜索关键词: "I2C-bus specification UM10204"

总结

I2C协议虽然简单,但包含了丰富的特性和严格的时间要求。深入理解协议的每个细节是设计稳定可靠I2C系统的基础。

4092

4092

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?