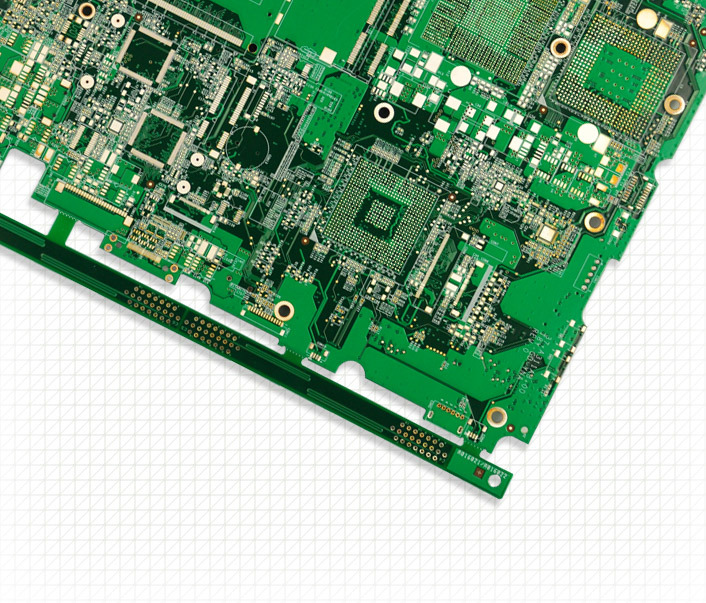

PCB布线与布局直接影响电路性能、可靠性和EMC特性。我们系统梳理20条核心规则,涵盖隔离设计、电源管理、信号完整性等关键领域,助你规避设计陷阱,提升研发效率。

一、隔离设计:降低干扰的底层逻辑

-

六类隔离准则

• 强弱电流:>1A电源线与小信号线间距≥3mm,防止磁场耦合导致传感器信号漂移。• 数字/模拟隔离:地平面分割+单点接地,电源入口并联1-2nF电容。例如某ADC电路整改后,地平面分割使信噪比提升20dB。

• 高频/低频分区:射频模块与MCU之间设置0.5mm宽地线隔离带,减少串扰。

-

空间布局策略

• 高速、中速、低速电路分区布局,间距≥50mm。• 输入/输出端口远离敏感区域,例如USB接口距时钟电路>20mm。

二、关键元件布局:晶振与时钟信号处理

-

晶振布局三原则

• 距离控制:晶振距IC引脚≤10mm,走线宽度≥0.3mm。• 接地优化:外壳多点接地,周围每5mm布置接地过孔。

• 屏蔽设计:时钟线优先走内层,表层用GND铜箔包裹。

-

连接器设计要点

• 时钟信号连接器插针周围布置环形接地针,例如8针连接器配6个GND针。• 高速信号出口处增加共模扼流圈,抑制辐射噪声。

三、电源与地线设计:降低阻抗与噪声耦合

-

电源完整性策略

• 模拟/数字电源独立分层,间距≤0.2mm。大电流路径采用2oz厚铜,压降降低30%。• 多层板中电源层靠近地平面,例如6层板采用TOP-GND-Signal-PWR-GND-BOTTOM叠层。

-

地线处理技巧

• 单点接地:模拟/数字地在系统接地点汇接,电压不一致时跨接1-2nF电容。• 母板设计:插板式PCB的母板需独立分割模拟/数字地,避免共地干扰。

四、多层板设计:布线层与平面规划

-

层叠结构优化

• 推荐结构:信号层紧邻地平面,例如4层板采用TOP-GND-PWR-BOTTOM。• 敏感信号层(如DDR布线)优先靠近地平面,减少信号回流路径。

-

数字/模拟分层策略

• 有条件时数字/模拟电路分置于不同层,同层时采用2mm开槽或加铺隔离地线。• 混合信号板中,高频数字信号(如PCIe)与模拟音频线路垂直交叉走线。

五、信号完整性:从布线到抗干扰设计

-

布线规则

• 线长控制:时钟线长度误差<5ps/inch,蛇形绕线间距≥3倍线宽。• 直角规避:高速信号线采用45°或圆弧转角,减少阻抗突变。

-

抗干扰措施

• 环路面积:关键信号环路≤20mm²,采用双绞线降低辐射。• 线间距:干扰源与敏感线间距≥2倍线宽,或正交走线。例如24GHz雷达模块中,差分线间距增加至0.2mm,串扰降低40%。

PCB布线与布局是功能实现与可靠性保障的核心环节。从隔离设计到信号优化,每项规则都需结合具体场景灵活应用。

481

481

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?