1.1、赋值

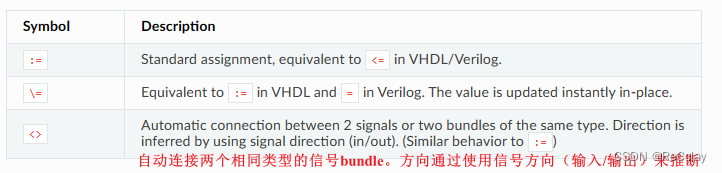

有多个赋值运算符:

当进行复用时(例如使用 when),最后一个有效的标准分配将获胜。否则,向同一受让人分配两次会导致分配重叠(overlap )。

val a, b, c = UInt(4 bits)

a := 0

b := a

//a := 1 // assignment overlap with a := 0

c := a

var x = UInt(4 bits)

val y, z = UInt(4 bits)

x := 0

y := x // y read x with the value 0

x \= x + 1

z := x // z read x with the value 1

// Automatic connection between two UART interfaces.

uartCtrl.io.uart <> io.uart

它还支持Bundle赋值。使用()将多个信号捆绑在一起进行赋值。

val a, b, c = UInt(4 bits)

val d = UInt(12 bits)

val e = Bits(10 bits)

val f = SInt(2 bits)

val g = Bits()

(a, b, c) := B(0, 12 bits)

(a, b, c) := d.asBits

(a, b, c) := (e, f).asBits

g := (a, b, c, e, f).asBits

在SpinalHDL中,理解一个信号的本质(组合/时序)是通过其声明来定义的,而不是通过它被赋值的方式。所有数据类型实例都将定义一个组合信号,而使用Reg(…)包装的数据类型实例将定义一个时序(寄存器)信号。

val a = UInt(4 bits) // Define a combinational signal

val b = Reg(UInt(4 bits)) // Define a registered signal

val c = Reg(UInt(4 bits)) init(0) // Define a registered signal which is set to 0 when a reset occurs

1.2、宽度检查

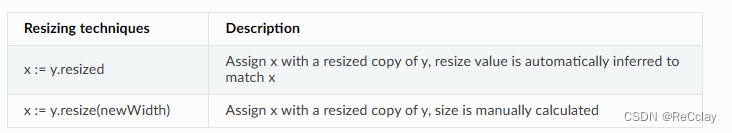

SpinalHDL 检查赋值语句左右两侧的位数是否匹配。有多种方法可以调整给定 BitVector(Bits、UInt、SInt)的宽度:

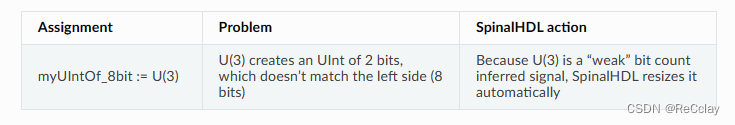

有一种情况,Spinal会自动调整值的大小:

1.3、组合逻辑环路

SpinalHDL 检查您的设计中是否存在组合逻辑环路(锁存器)。如果检测到其中一个,它会引发错误并且 SpinalHDL 将打印出该环路的路径。

文章详细介绍了SpinalHDL中的赋值机制,包括复用时的赋值规则和赋值重叠问题。此外,讨论了宽度检查的重要性,以及如何在不匹配时调整BitVector的宽度。文章还强调了SpinalHDL对组合逻辑环路的检查,指出环路会导致错误并提供诊断信息。

文章详细介绍了SpinalHDL中的赋值机制,包括复用时的赋值规则和赋值重叠问题。此外,讨论了宽度检查的重要性,以及如何在不匹配时调整BitVector的宽度。文章还强调了SpinalHDL对组合逻辑环路的检查,指出环路会导致错误并提供诊断信息。

490

490

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?