一、Stream类简介

SpinalHDL的lib中提供了一个Stream类,这个类继承自SpinalHDL的Bundle类,支持Master/Slave,携带数据,因此主要包括三个信号:valid、ready、payload。

这三个信号可以构成最简单的握手接口,满足大部分情况下的module间交互。接下来介绍其中的一些方法,与Verilog中写简单握手的方法一一对应。

1.1 Stream的方向定义

val io = new Bundle{

val data_in = slave Stream(UInt(8 bits))

val data_out = master Stream(UInt(8 bits))

}

上图为一个流水级寄存器的io信号示例,data_in为模块输入,则对于简单握手协议来说本模块是接收数据的slave,因此data_in作为一个Stream类包含的三个信号及其方向分别为:valid(in)、ready(out)、payload(in)。

反之,data_out为模块输出,其包含的三个信号及其方向分别为:valid(out)、ready(in)、payload(out)。

1.2 Stream实现简单握手时序

一个典型的简单握手时序如图所示,上级的valid与payload同时产生,直至下级ready拉高,实现上级valid与下级ready同时为高时握手成功。valid只有在握手成功的下一拍才允许拉低,若握手失败,则valid需保持为高。

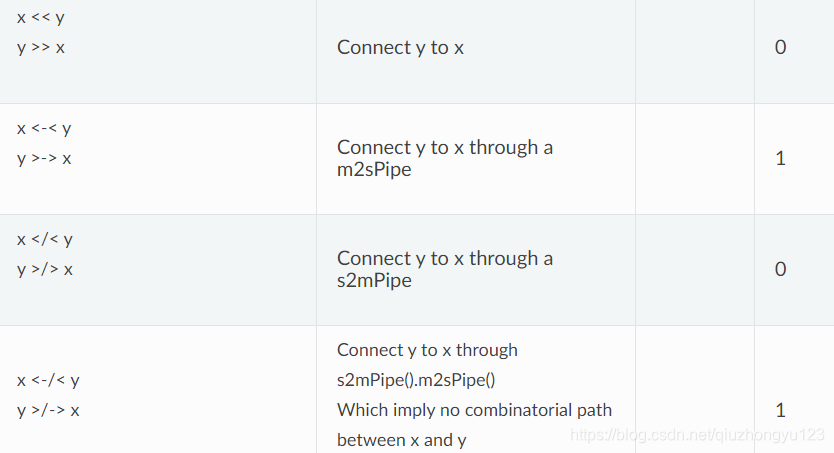

在SpinalHDL的document中,给出了上述的几种连接方式。那么在SpinalHDL中,data_in和data_out应如何连接才能实现上图的握手时序呢?

由于要实现寄存器打拍的效果,那么必须选择latency为1的连接方式。①和③两种latency为0的连接方式显然不能满足。其中x << y或y >> x就相当于是使用Verilog中的assign赋值语句。

而②可以实现打拍的连接方式,并且自动完成了本级valid、payload的时序逻辑赋值和ready的组合逻辑赋值。<-<看似一个赋值保留字,其实是Stream的一个方法:

/*Connect that to this. The valid/payload/ready path are cut by an register stage */

/* Connect that to this. The valid/payload path are cut by an register stage */

def <-<(that: Stream[T]): Stream

本文介绍了SpinalHDL的lib中Stream类,它继承自Bundle类,包含valid、ready、payload三个信号,可构成简单握手接口。文中阐述了Stream的方向定义、实现简单握手时序的方法,还探讨了valid赋值条件不止握手成功以及payload经组合逻辑传递时的处理方式,强调阅读源码的重要性。

本文介绍了SpinalHDL的lib中Stream类,它继承自Bundle类,包含valid、ready、payload三个信号,可构成简单握手接口。文中阐述了Stream的方向定义、实现简单握手时序的方法,还探讨了valid赋值条件不止握手成功以及payload经组合逻辑传递时的处理方式,强调阅读源码的重要性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1251

1251

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?