文章目录

在摩尔定律不太适用的今天,人们试图增加CPU核数以提升系统整体性能。这类系统称之为多核系统(简称MP,Multi-Processor)。我们知道每个CPU都有一个私有的L1 Cache(不细分iCache和dCache)。假设一个2核的系统,我们将会有2个L1 Cache。这就引入了一个问题,不同CPU之间的L1 Cache如何保证一致性呢?首先看下什么是多核Cache一致性问题。

1、多核一致性问题背景

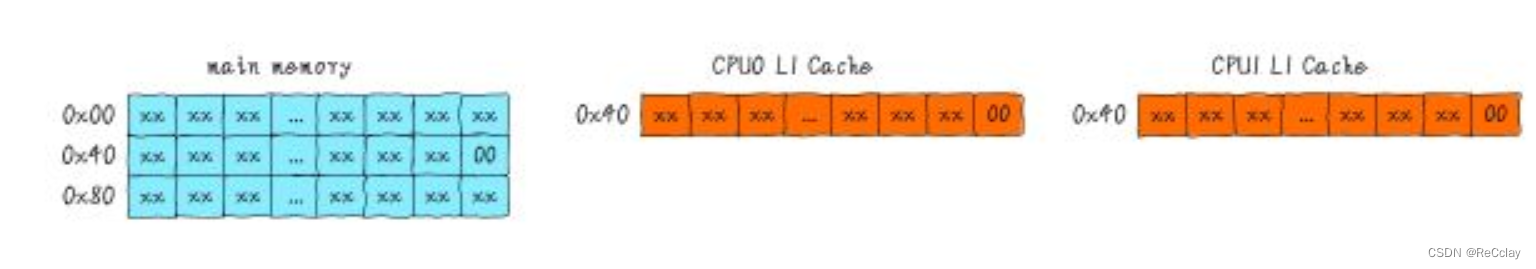

首先我们假设2个CPU的系统,并且L1 Cache的cache line大小是64 Bytes。两个CPU都读取0x40地址数据,导致0x40开始的64 Bytes内容分别加载到CPU0和CPU1的私有的cache line。

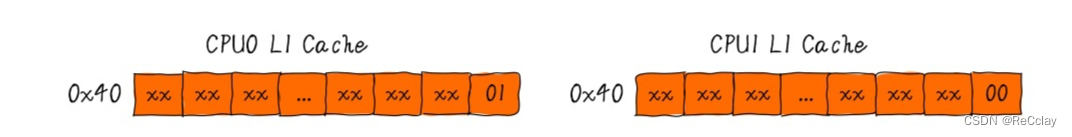

CPU0执行写操作,写入值0x01。CPU0私有的L1 Cache更新cache line的值。然后,CPU1读取0x40数据,CPU1发现命中cache,然后返回0x00值,并不是CPU0写入的0x01。这就造成了CPU0和CPU1私有L1 Cache数据不一致现象。

按照正确的处理流程,我们应该需要以下两种方法<

本文介绍了多核系统中遇到的Cache一致性问题,并详细讲解了Bus Snooping Protocol和MESI协议的工作机制,重点阐述了MESI协议如何通过状态机减少带宽压力,确保数据一致性。

本文介绍了多核系统中遇到的Cache一致性问题,并详细讲解了Bus Snooping Protocol和MESI协议的工作机制,重点阐述了MESI协议如何通过状态机减少带宽压力,确保数据一致性。

订阅专栏 解锁全文

订阅专栏 解锁全文

566

566

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?