文章目录

分析

非整数倍的数据位宽转换题型解题思路:(整数倍位宽同样适用)

- 第一,找最小公倍数,确定计数周期,确定输出时刻。在每次valid有效的时钟下,cnt自增1。如8->12,最小公倍数24,那么相当于计数输入3个周期,输出在输入的第1个计数周期和第2个计数周期(即:cnt=1;cnt=2时)。

- 第二,找输入输出最大倍数关系,确定缓冲区大小。最大倍数就是直接相除,比如24->128,最大倍数为5,则中间缓存大小为245=120;8->12,最大倍数为1,中间缓存大小为81=8。

- 第三,使用拼接运算符,拼接缓冲区buff和输入data_in来输出,同时将未输出的data_in保存在缓存buff。

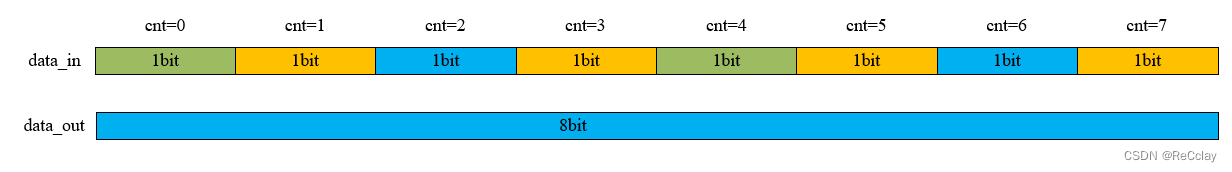

题目0(串转并,1bit转8bit)

其实仔细想一下,我们的串转并电路不也是窄到宽的位宽转换电路么?这里以1bit转8bit为例写一下程序。

题解0

module

订阅专栏 解锁全文

订阅专栏 解锁全文

878

878

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?