理想流水线一般指流水线中不存在冲突或冒险(Hazzard)问题、不存在资源冲突,且进入流水线的指令相互之间不存在依赖关系或相关关系。

单周期数据通路改造为三级流水

通过修改单周期CPU的数据通路,可以实现简易流水线CPU的设计。

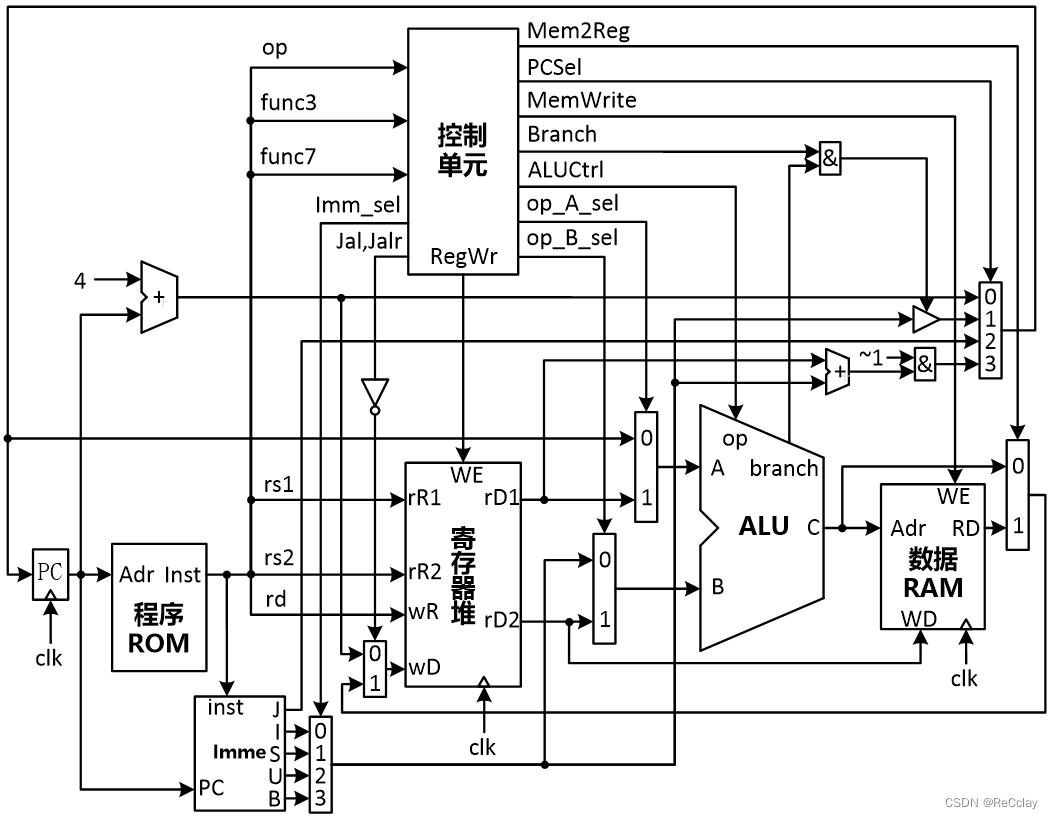

以下以图2-1所示的单周期CPU为例,介绍如何将单周期CPU改造成“取指-译码-执行”的三级理想流水CPU。

图2-1 单周期CPU数据通路示例

STEP1:分割单周期CPU数据通路

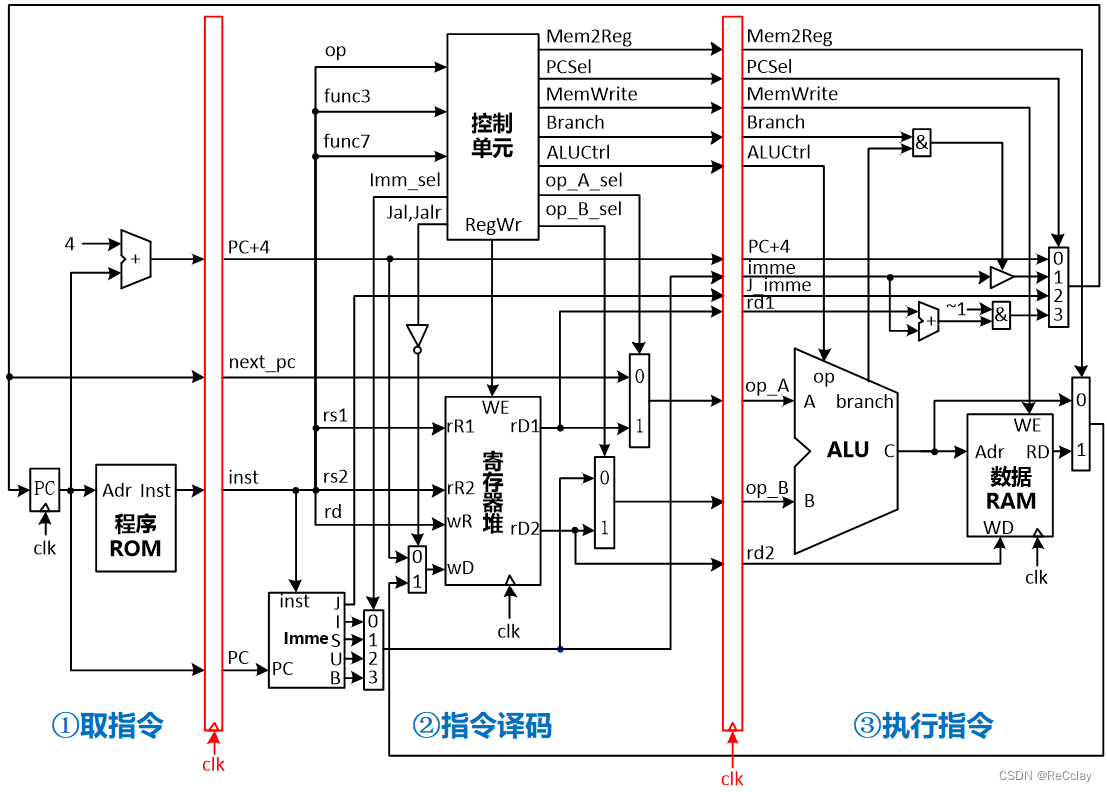

第一步,根据目标流水线的阶段构成,分割单周期CPU的数据通路,并在分割处加入流水线段寄存器,将各阶段之间的接口信号缓存起来,如图2-2所示。

图2-2 分割单周期CPU数据通路

STEP2:修改PC逻辑

第二

本文介绍了将单周期CPU改造成理想流水线CPU的过程,包括分割数据通路、修改PC逻辑和调整写回逻辑。通过这三个步骤,实现了无冲突、资源无争用的三级流水线(取指-译码-执行),优化了指令执行效率。

本文介绍了将单周期CPU改造成理想流水线CPU的过程,包括分割数据通路、修改PC逻辑和调整写回逻辑。通过这三个步骤,实现了无冲突、资源无争用的三级流水线(取指-译码-执行),优化了指令执行效率。

订阅专栏 解锁全文

订阅专栏 解锁全文

854

854

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?