复位电路基础

复位电路是每个数字逻辑电路中最重要的组成部分之一。复位电路的工作日的有两个方面:第一是仿真的时候使电路进入初始状态或者其他预知状态;第二是对于综合实现的真实电路,通过复位使电路进入初始状态或者其他预知状态。一般来说,逻辑电路的任何一个寄存器、存储器结构和其他逻辑单元都必须要附加复位逻辑电路,以保证电路能够从错误状态中恢复,可靠地工作。

思考:哪些电路没有复位信号?

- 通常来说,时序电路属于双稳态电路,上电之后必须要有一个初始态,才可以正常工作,所以时序电路必须有复位信号;而组合逻辑电路没有存储功能,因此不需要复位信号。

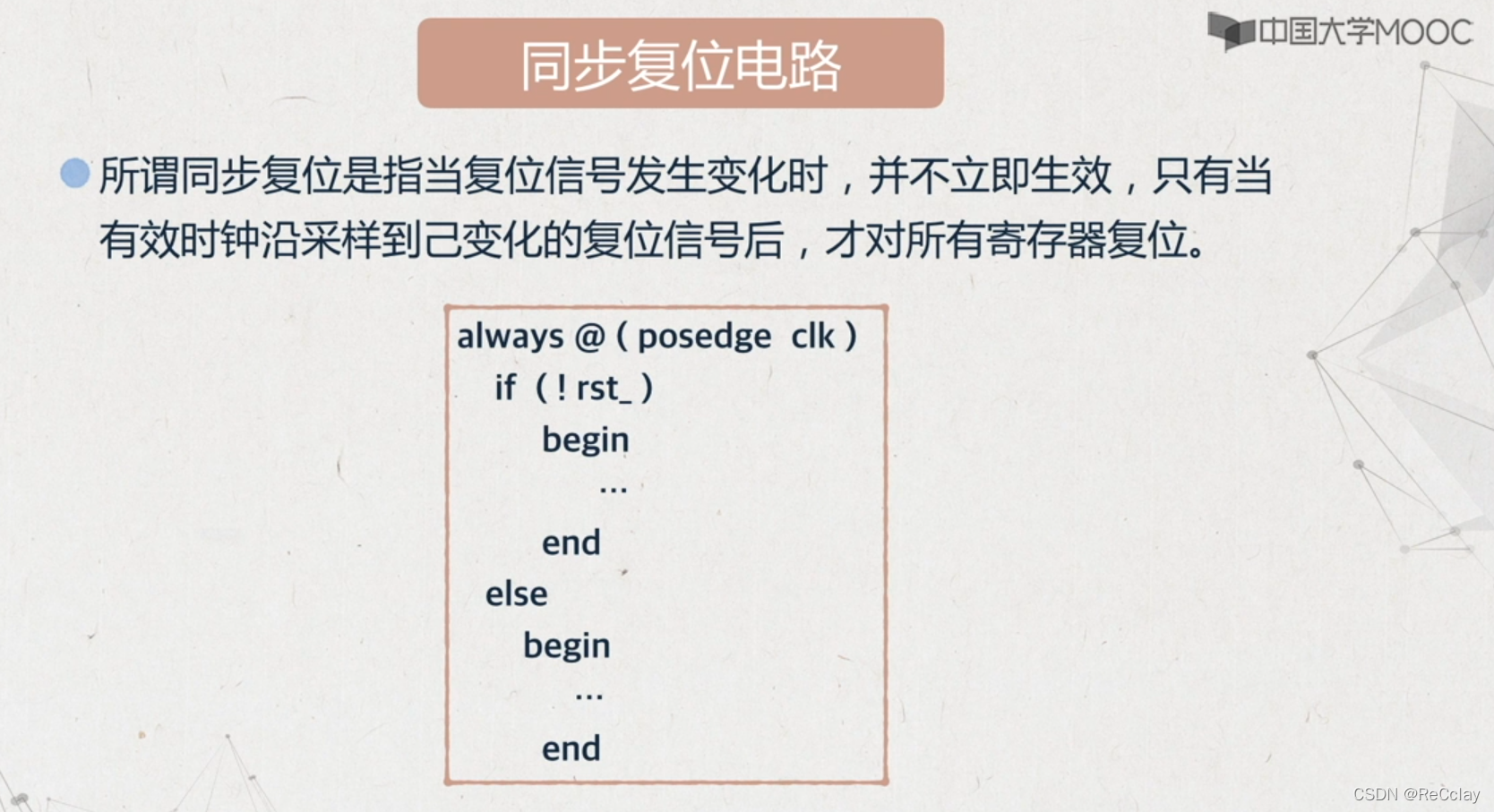

同步复位电路

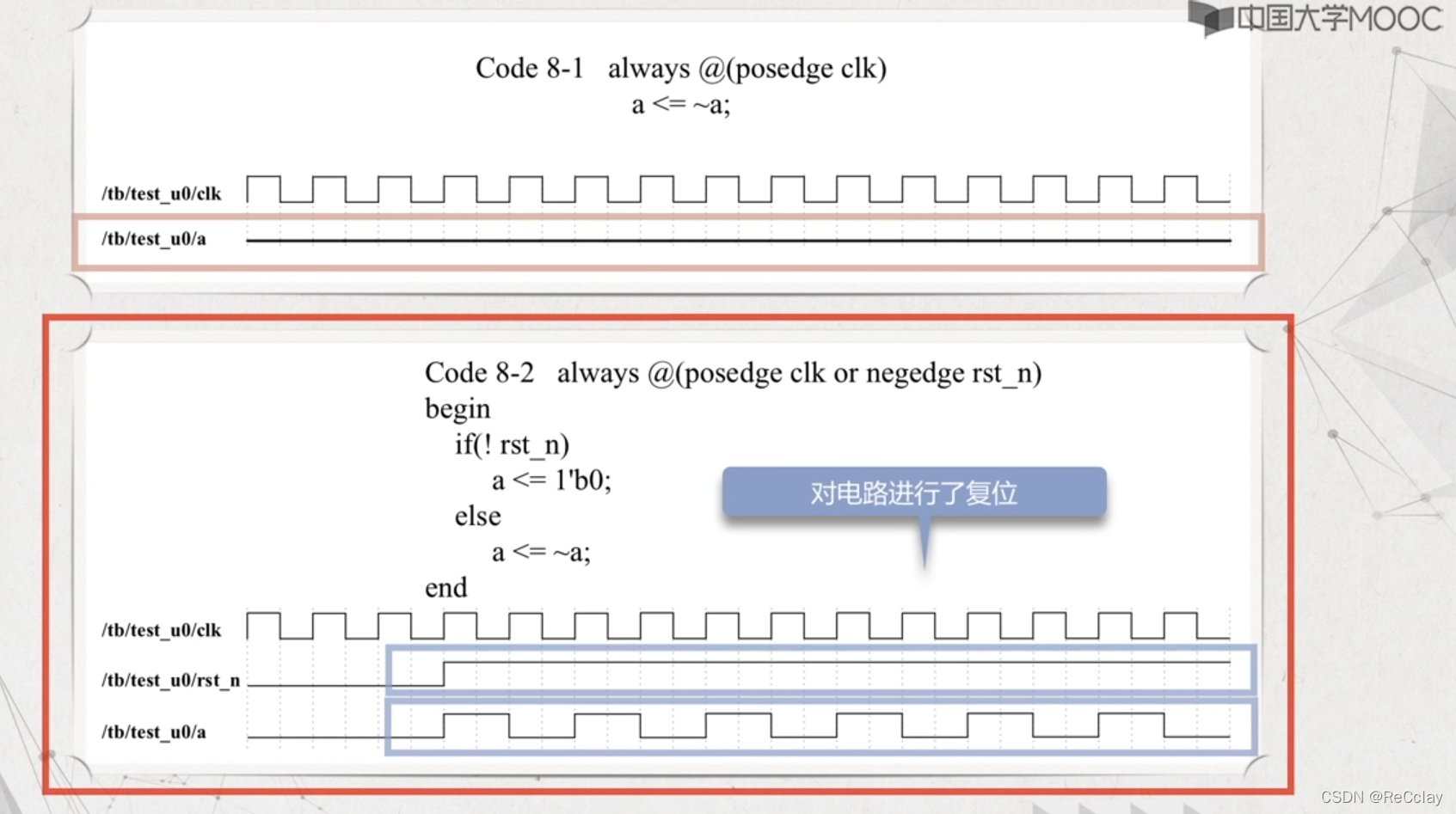

复位有两种方式,同步复位和异步复位。 所谓同步复位是指当复位信号发生变化时,并不立即生效,只有当有效时钟沿采样到已变化的复位信号后,才对所有寄存器复位。

本文深入探讨复位电路的基础,包括同步复位和异步复位的优缺点。推荐采用"异步复位,同步释放"的设计方案以避免亚稳态问题。同步复位需保证复位信号有效时间足够,而异步复位能快速复位,但可能受毛刺影响。复位网络采用树形拓扑结构确保信号同步。

本文深入探讨复位电路的基础,包括同步复位和异步复位的优缺点。推荐采用"异步复位,同步释放"的设计方案以避免亚稳态问题。同步复位需保证复位信号有效时间足够,而异步复位能快速复位,但可能受毛刺影响。复位网络采用树形拓扑结构确保信号同步。

订阅专栏 解锁全文

订阅专栏 解锁全文

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?