一,AXI HP总线描述

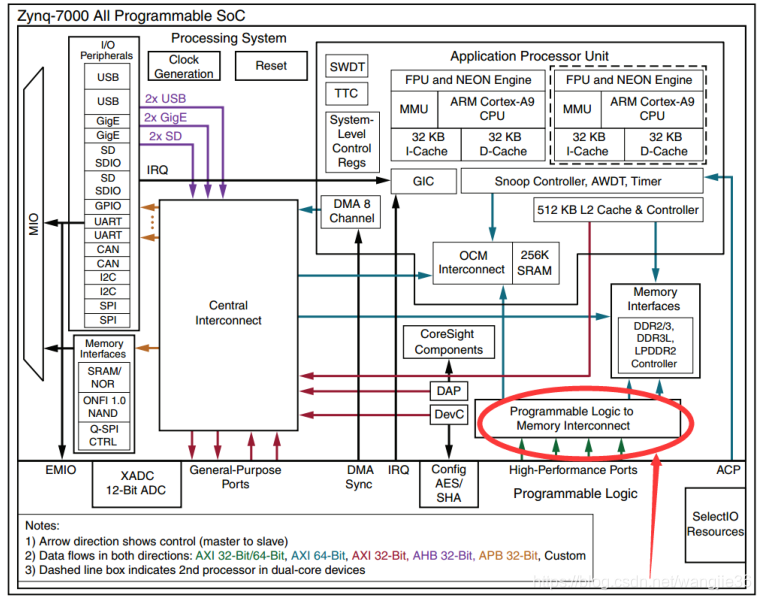

经常需要将PS端处理结果实时送到PL端处理,或者将PL端的大量数据实时送到PS端处理,常规我们会想到使用DMA的方式来进行,但是各种协议非常麻烦,灵活性也比较差。ZYNQ一共有4路HP 口,HP口是AXI Slave 设备,我们可以通过这4路HP接口实现高带宽的数据交互在vivado的界面中 HP的配置如下图(HP0~HP3),这里面有使能控制,数据位宽选择,可选择32bit或64bit的位宽。

AXI4 所采用的是一种 READY,VALID 握手通信机制,即主从模块进行数据通信前,先根据操作对各所用到的数据、地址通道进行握手。主要操作包括传输发送者 A 等到传输接受者B的 READY 信号后,A 将数据与 VALID 信号同时发送给 B,这是一种典型的握手机制。

AXI 总线分为五个通道:

读地址通道,包含 ARVALID, ARADDR, ARREADY 信号;

写地址通道,包含 AWVALID,AWADDR, AWREADY 信号;

读数据通道,包含 RVALID, RDATA, RREADY, RRESP 信号;

写数据通道,包含 WVALID, WDATA,WSTRB, WREADY 信号;

写应答通道,包含 BVALID, BRESP, BREADY 信号;

系统通道,包含:ACLK,ARESETN 信号;

本文介绍了如何利用ZYNQ的四路HP总线进行高带宽数据交互,避免使用复杂的DMA协议。通过AXI4的READY、VALID机制详细阐述了读写操作流程。在Vivado工程配置中,设置了HP总线的频率和数据宽度,并通过VIO IP核控制读写通道。测试结果显示,每路HP总线的读写带宽接近,但多通道切换导致的地址切换开销可能影响单通道带宽。

本文介绍了如何利用ZYNQ的四路HP总线进行高带宽数据交互,避免使用复杂的DMA协议。通过AXI4的READY、VALID机制详细阐述了读写操作流程。在Vivado工程配置中,设置了HP总线的频率和数据宽度,并通过VIO IP核控制读写通道。测试结果显示,每路HP总线的读写带宽接近,但多通道切换导致的地址切换开销可能影响单通道带宽。

订阅专栏 解锁全文

订阅专栏 解锁全文

3438

3438