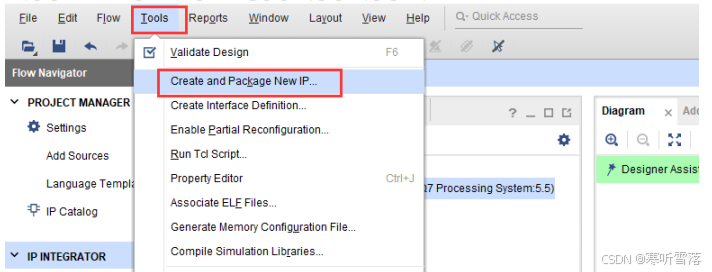

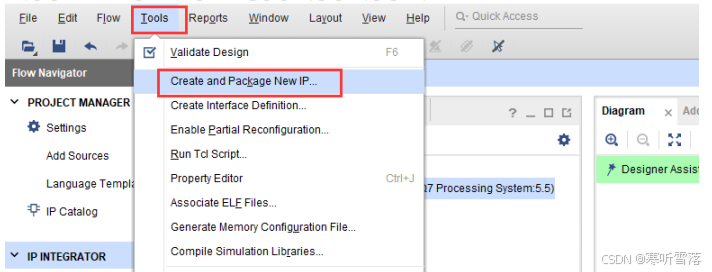

创建自定义

IP

核,在菜单栏中点击“

Tools

”,在弹出的列表中选择 “Create and Package New IP

”

在弹出的对话框中点击“

Next

”,之后在下图所示的界面中选择“

Create a new AXI4 peripheral”,点击“

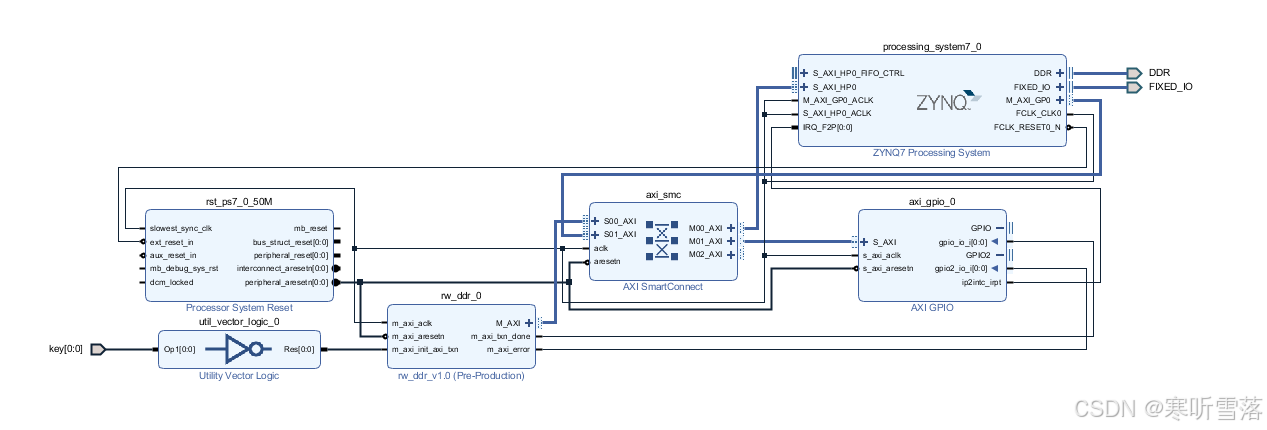

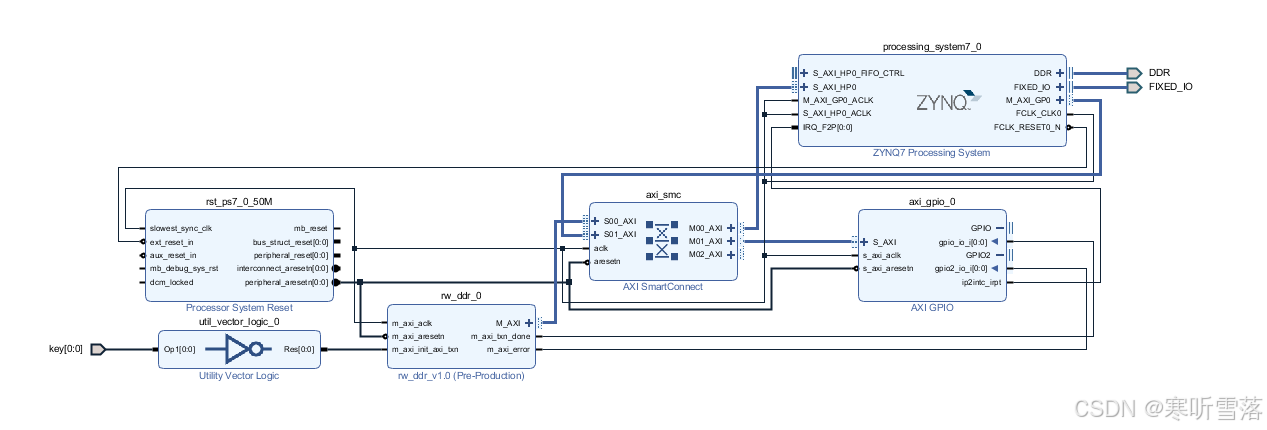

本文探讨了如何利用FPGA的硬件描述语言(HLS)设计IP模块,实现浮点数运算的加速。在面对大量浮点运算任务时,将这些计算任务卸载到FPGA上,可以显著减少CPU的负载。具体实现中,CPU指定浮点数据的存储地址和长度,IP模块计算平均值,并通过中断机制通知CPU计算完成。

本文探讨了如何利用FPGA的硬件描述语言(HLS)设计IP模块,实现浮点数运算的加速。在面对大量浮点运算任务时,将这些计算任务卸载到FPGA上,可以显著减少CPU的负载。具体实现中,CPU指定浮点数据的存储地址和长度,IP模块计算平均值,并通过中断机制通知CPU计算完成。

957

957

2168

2168