一,verilog方式《------》PS GP

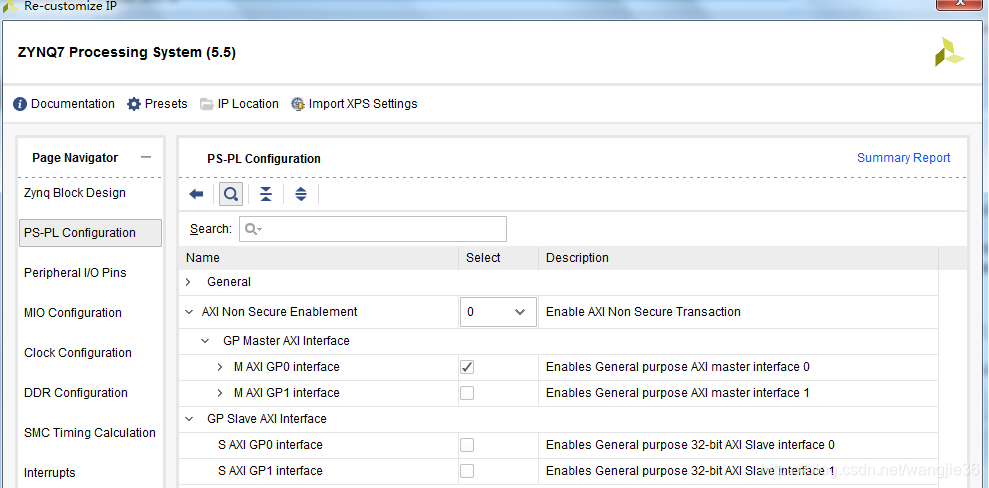

1,PL端的AXI GP的从机,实现PS端可读写访问的AXI GP寄存器外设。对Processing System配置页面做更改。选中PS-PL Configuration项,展开AXI Non Secure Enablement--> GP Master AXI Interface,勾选M AXI GP0 interface,相当于开启 PS 系统的 AXI GP0 的主机功能。

注意:下面还有一个M AXI GP1 interface,也就是说 Zynq 最多可以有2个AXI GP主机外设。

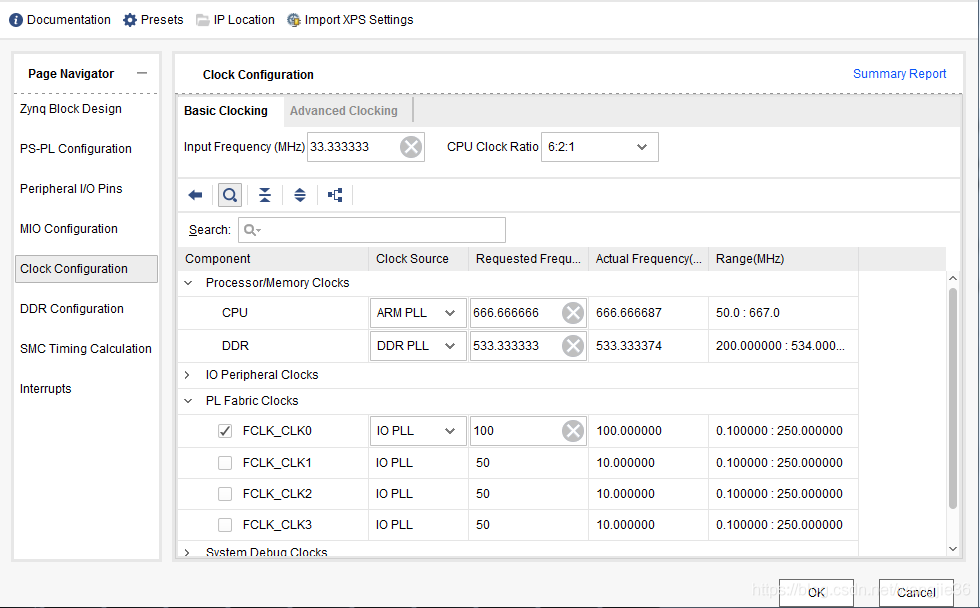

2,然后,在 Clock Configuration 项,展开 PL Fabric Clocks,勾选FCLK_CLK0,设定时钟频率为100(MHz)。这个由PS引出的时钟将要作为AXI GP的工作时钟。

3,完成 ZYNQ7 Processing System 的配置更改后,回到 Diagram 界面中,可以看到新出现了名为 M_AXI_GP0_ACLK、M_AXI_GP0 和 FCLK_CLK0 的接口,下面我们要对这些接口进行连接或引出。先点击选中

本文介绍了如何通过Verilog实现ZYNQ GP总线的PS与PL交互,包括配置PS GP、设置时钟、创建接口、地址分配、连接信号,以及ILA逻辑分析仪的使用,涉及AXI GP从机接口设计和ILA在线调试。

本文介绍了如何通过Verilog实现ZYNQ GP总线的PS与PL交互,包括配置PS GP、设置时钟、创建接口、地址分配、连接信号,以及ILA逻辑分析仪的使用,涉及AXI GP从机接口设计和ILA在线调试。

订阅专栏 解锁全文

订阅专栏 解锁全文

1950

1950