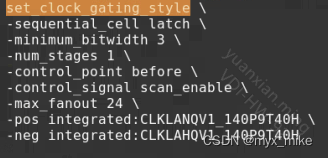

DC综合设置clock-gating-style

这个set_clock_gating_style是要设置在DC的compile/conpile_ultra之前。

注意,这里的-control_signal scan_enable,这里可以用-control_signal test_mode,但必须要这个设置放在DC的compile/conpile_ultra之前。

这里使用-control_signal test_mode的test-coverage没有scan_enable的test-coverage高。

如果要让-control_signal test_mode的test-coverage更高,需要加个-obervation_point true的option。但是,这个-obervation_point true的option又不能再用integrated_latch作为clock-gating cell。

注意,observation point logic是接在clock-gating cell内部的,集成式integrated-latch的clock-gating cell就会接不进去这个observation point logic,就必须用组装式的clock-gating cell。

本文介绍了在DC综合设置中,如何正确配置clock-gating-style,特别是控制signal的test_mode与scan_enable的区别。为了提高test_mode的覆盖率,需添加observation_point,但需注意integrated_latch与clock-gatingcell的兼容性问题,可能需要选择assembly-style的clock-gatingcell。

本文介绍了在DC综合设置中,如何正确配置clock-gating-style,特别是控制signal的test_mode与scan_enable的区别。为了提高test_mode的覆盖率,需添加observation_point,但需注意integrated_latch与clock-gatingcell的兼容性问题,可能需要选择assembly-style的clock-gatingcell。

987

987

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?