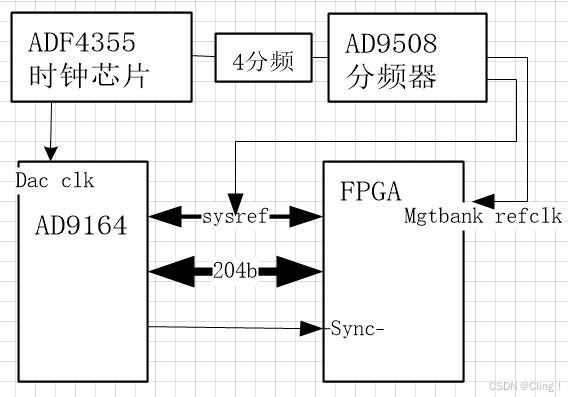

本次工程以2.5G采样时钟为列,工程主要架构分为ADF4355(时钟芯片)、AD9508(分频器)、AD9164(DAC)、FPGA。如图所示;

本工程的重点在于,ADF4355、AD9164的寄存器配置,以及各时钟的计算。

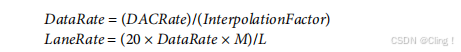

以2.5G的时钟为例,各时钟计算公式如下:

这里插值系数为1(InterpolationFactor)、转换器数量为1(M)、X8(L),可以得出LaneRate为6.25Gbps。以上值可以 修改。

发送数据的时钟为:6.25/40 = 156.25Mhz 。(用户位宽为32,8B10B编码后为40)。

Sysref时钟用户数据帧同步公式如下:

Fbitrate为线速率(6.25),F 为每帧的八 位字节数,K 为每个多帧块的帧数,而 n 则为任意正数。当F(1)、K(32)、N(4),Sysref为4.8828125Mhz。

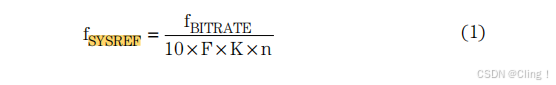

ADF4355寄存器配置。该芯片配置接口为SPI接口,原理与上篇LMX类似主要配置分频系数等参数可以参考官方评估软件。如图:

配置好后按照按R12—R0的顺序利用SPI接口写入即可。

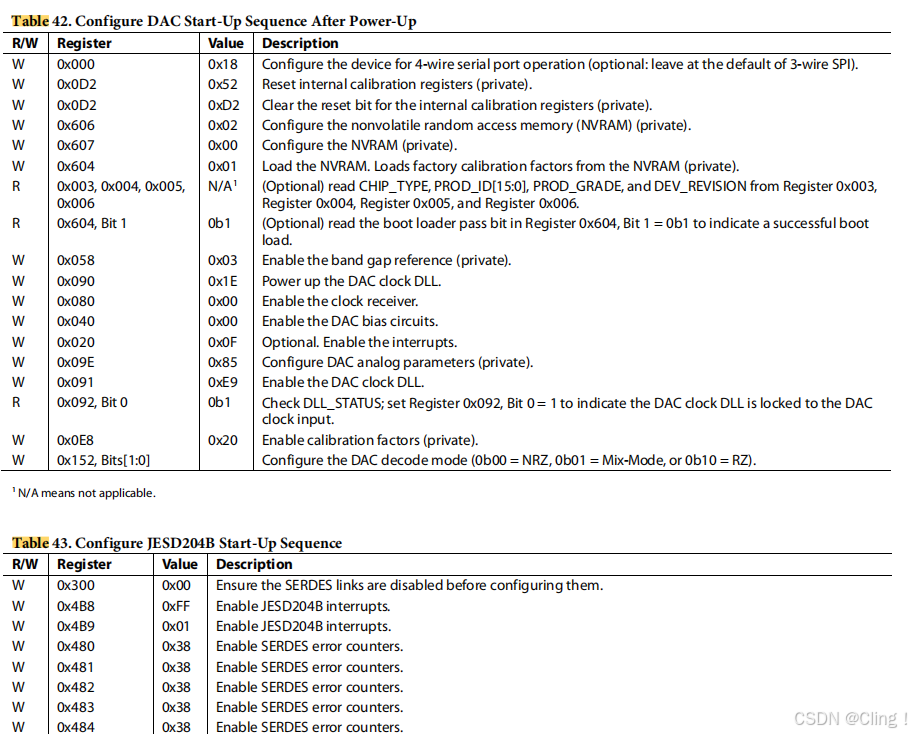

AD9164寄存器配置参考手册Page71:

本次工程只对Table42、Table43配置(没有使用的寄存器按默认值写入即可)。没用到NCO所以对Table44没做配置。

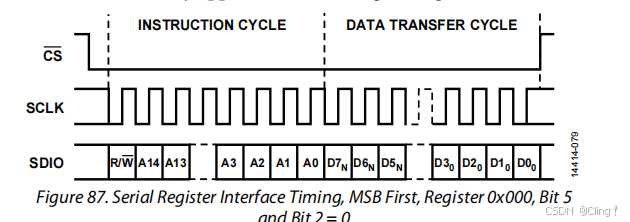

AD9164的SPI的时序如图:

568

568

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?