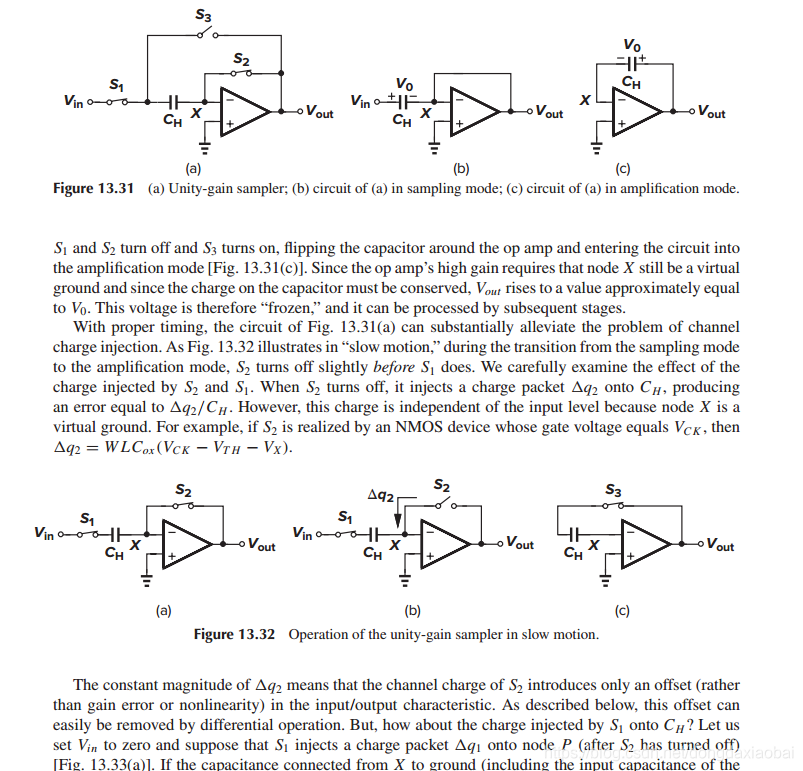

开关电容的开关顺序是有讲究的。如图(Razavi教材模拟cmos设计第二版556页)中的电路,一般总是先断开与运放相连的开关(S2),再断开和信号相连的开关(S1)。原文对此的解释是:由于运放虚地特性,输入端X是地,S2断开时注入的电荷和信号无关,成为一个固定的offset. (中文翻译好像是避免非线性电荷注入,也就是注入的电荷量恒定。)

这个解释咋一看似乎没什么问题,但实际上如果用下方的(a)(b)(c)图会有一点歧义。注意按照(b)图的画法,S2断开以后运放已经变成了开环,那么这一注入的电荷无疑会使输入端X的电压不再为0。由于运放增益很高,假定开关尺寸很大,而采样电容很小,这个电荷导致的X点电位变化完全可能达到相当可观的量,经过运放导致输出产生很大的swing。如果是实际的运放,无法handle large swing, 那么当做‘offset’显然不完全合适。

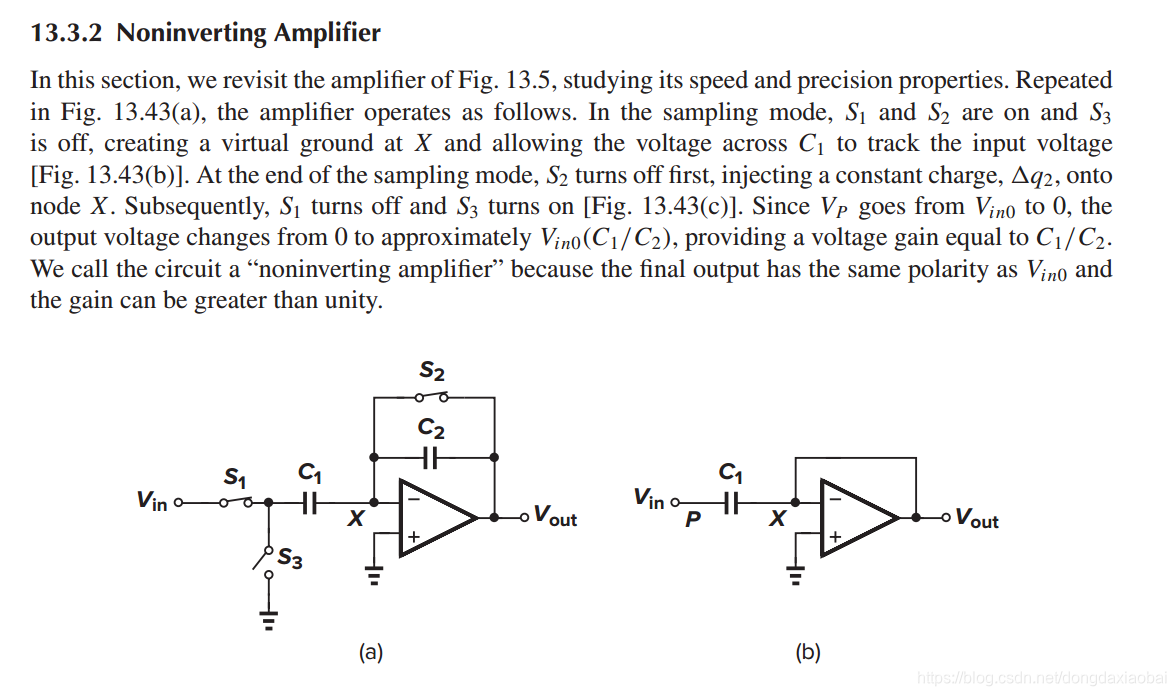

当然,教材的解释并不能说是错误的。因为并不能规定offset是1uV,1mV还是100V。个人理解是对于实际电路,运放只允许在不同开关切换的non-overlap短暂时间内变成开环。而多数时候我们总是保证电路工作在闭环状态,这样才能使运放的输入端维持虚地特性。仍然以教材上的开关电容放大器为例:

在这里,运放要么输入输出短接,要么通过电容C2反馈,总之始终保持闭环状态。当S2断开时,假定X点产生了很大的电压,那么运放的输出端迅速变化,导致C2上的电荷发生改变。由于电荷守恒,最终运放会settle到末态。这一settle过程的最终效果是使得少量的injection电荷主要被C2吸收,而不影响X点的虚地特性以及C1上的电荷。

那么对于C1而言,S1断开的瞬间同样会有charge injection的影响。由于此时S2已经断开,运放的输入端浮空,这一电荷无法注入两个电容中。注意到C1下方还有S3。实际上S1断开以后,C1的下极板的下一个状态就是通过S3接地。这样一来,即使有charge injection,最终也是因电荷守恒被抵消,不影响最终的输出。

反过来,如果S1先于S2断开。那么S1断开时的电荷就会实实在在地注入C1中,从而影响采样值的准确性。

由此回到13.32(c),这里面同样出现了S3。这里的S3在S1断开后接入。这样一来运放实际上断开的时间只有S2和S3的non-overlap时间。由于实际运放带宽有限,短暂的切换过程中运放各点的电压还无法瞬变,就重新闭环。因此S2引入的charge就产生的电压。如果

足够小,可以视为residual-offset。(这个结构本身是cds,抵消了运放自身的offset)基于它的signal-independent特点,改成全差分的结构便可以很好地抵消其影响。

总结:

1.开关电容的运放需要保持闭环才能保证输入端的虚地特点。而输入端的'虚'地是电荷守恒计算的关键;

2.电容的下极板永远连在低阻点上,才能保证最终settle到想要的结果。

********************************************************************************************************************

以上想法系本猹在Leo 狮兄启示下的一点收获。由此看来razavi大佬可能跳步了。开关电容这里面的水很深,本猹太年轻,还把握不住,以上想法仅供参考。

开关电容的开关顺序对电荷注入有显著影响。先断开与运放连接的开关(S2)可以保持输入端的电荷不变,避免非线性电荷注入。然而,在开环状态下,电荷注入可能导致运放输出大的摆幅。保持闭环状态能确保运放输入端的虚地特性,并通过电荷守恒抵消注入电荷的影响。S1断开时,若S3已接地,C1的电荷注入会被抵消,反之则会影响采样精度。开关电容设计中的电荷注入和闭环操作是关键考虑因素。

开关电容的开关顺序对电荷注入有显著影响。先断开与运放连接的开关(S2)可以保持输入端的电荷不变,避免非线性电荷注入。然而,在开环状态下,电荷注入可能导致运放输出大的摆幅。保持闭环状态能确保运放输入端的虚地特性,并通过电荷守恒抵消注入电荷的影响。S1断开时,若S3已接地,C1的电荷注入会被抵消,反之则会影响采样精度。开关电容设计中的电荷注入和闭环操作是关键考虑因素。

2837

2837

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?