目录

锁相环(Phase-Locked Loop, PLL)是一种反馈控制系统,广泛应用于无线电通信、频率合成、时钟恢复、调制解调等领域,其核心功能在于使系统的输出信号频率和相位与输入参考信号保持一致。在Simulink中构建PLL模型,不仅有助于理解其工作原理,还能直观地观察和分析PLL的各项动态特性。

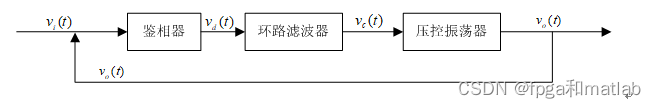

1.锁相环的基本原理

锁相环一般由三个基本部件组成:压控振荡器(VCO) 、环路滤波器(LF)以及鉴相器(PD)。在实际应用中有各种锁相环路,它们均由基本的环路变化而来的。

其中压控振荡器受控制电压的控制,使压控振荡器的振荡频率向参考信号的频率接近,两个信号间的相位差减小,直到消除频率差而锁定。环路滤波器的作用是滤除误差电中的高频成分和噪声,以保证环路所要求的性能,减少相位噪声,提高输出信号频率的精度。鉴相器是相位比较装置,它把输出信号相位和参考信号的相位进行比较,产生对应于两个信号相位差的误差电压。

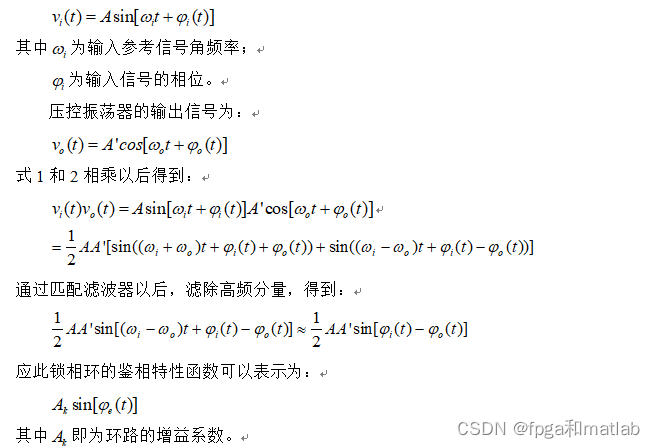

为了从最基础的原理介绍锁相环,我们这里使用模拟信号处理来推导锁相环的工作过程和原理,这里我们假设锁相环输入的信号为:

在环路跟踪状态下,相位误差较小,对正弦鉴相特性,当在区间[-pi/6,pi/6]时,可以认为鉴相特性处于线性区,合理设计的环路,其跟踪过程大部分处于这个区域。鉴相器的数学模型可以表示为:

![]()

2. PLL基本组成

PLL通常由以下四个主要部分构成:

- 鉴相器(Phase Detector, PD):比较输入信号与反馈信号的相位差,并产生误差信号。

- 环路滤波器(Loop Filter, LF):对鉴相器输出的误差信号进行低通滤波,以提取相位误差的直流分量,同时抑制噪声和高频干扰。

- 压控振荡器(Voltage-Controlled Oscillator, VCO):根据输入的控制电压调整输出信号的频率。

- 分频器(Divider, N)(可选):用于产生反馈信号,通过将VCO的输出信号频率降低到与参考信号相同的频率,以便与鉴相器比较。

PLL的数学模型可以用以下方程组表示:

- 鉴相器输出:误差信号e(t)通常与输入信号θin(t)和反馈信号θfb(t)的相位差成正比,假设为线性鉴相器,则有e(t)=Kp(θin(t)−θfb(t)),其中Kp是鉴相增益。

- 环路滤波器:环路滤波器的传递函数H(s)通常设计为低通滤波器,其输出u(t)为滤波后的误差信号,即U(s)=H(s)E(s),其中U(s)和E(s)分别是滤波器输出和误差信号的拉普拉斯变换。

- 压控振荡器:VCO的输出频率fout与控制电压u(t)的关系可近似为线性,即fout(t)=f0+Kvu(t),其中f0是VCO的自由振荡频率,Kv是压控增益。

- 闭环动态:考虑分频器的情况下,反馈信号频率为fb=fout/N,则整个PLL系统的闭环传递函数可表示为关于频率误差的传递函数,涉及鉴相器、环路滤波器和VCO的参数。

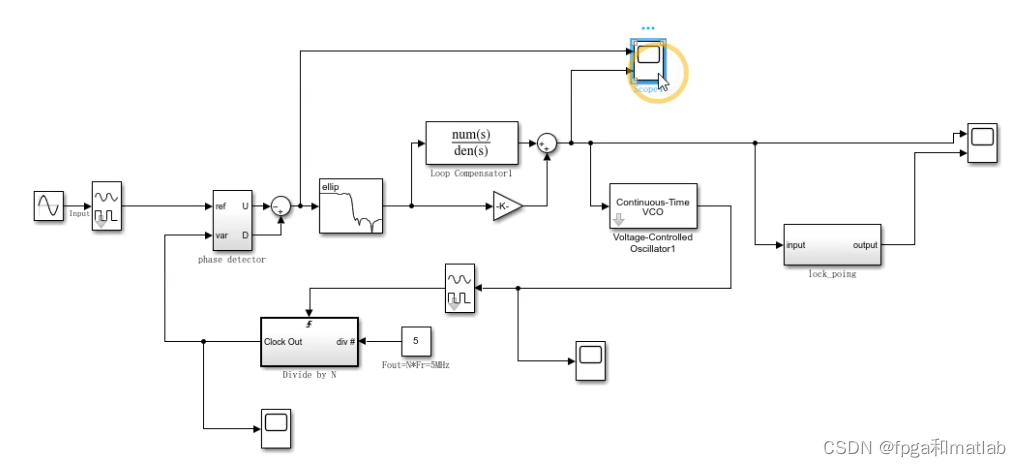

2.基于simulink的模拟锁相环控制直流电机速度仿真

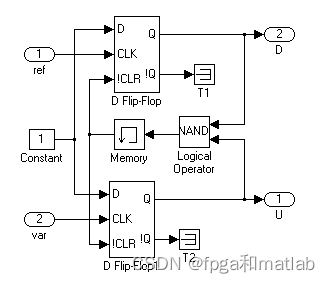

4097锁相环是一个相位负反馈控制系统,它主要由三部分组成,分别是鉴相鉴频器(PFD)、环路滤波器(LF)和电压控制器(VCO)。系统的基本结构如下所示:

下面我们对这个模型进行简单的介绍。

鉴相器的主要功能就是鉴别输入信号与输出信号的相位差,其作用就是误差提取功能。

在这里,鉴相器,我们主要通过D触发器来实现。

这个模块的主要功能就是起到异或的功能。只要两路信号有微小的差别,其误差就是计算出来。

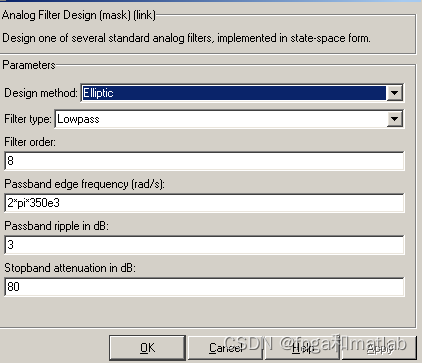

环路滤波器的主要功能就是滤除鉴相器的噪声部分以及高频分量。

在模拟PLL系统中,我们经常使用的是巴特窝斯模拟滤波器,其参数设置如下所示:

这里我们设置的是8阶滤波器。

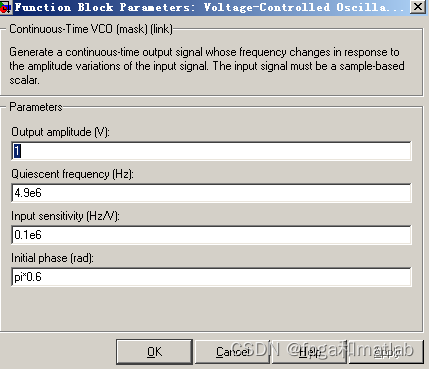

压控振荡器(Voltage-Controlled Oscillator)是一个电压—频率变换装置,振荡频率随输入控制电压Uc(t)线性地变化,即应有变换关系:

![]()

在Matlab中压控振荡器即表示为对连续信号的积分,它的输出信号的频率随着输入信号幅度的变化而发生相应的变化,其的工作原理通过下面的公式来描述:

![]()

其参数设置界面如上图

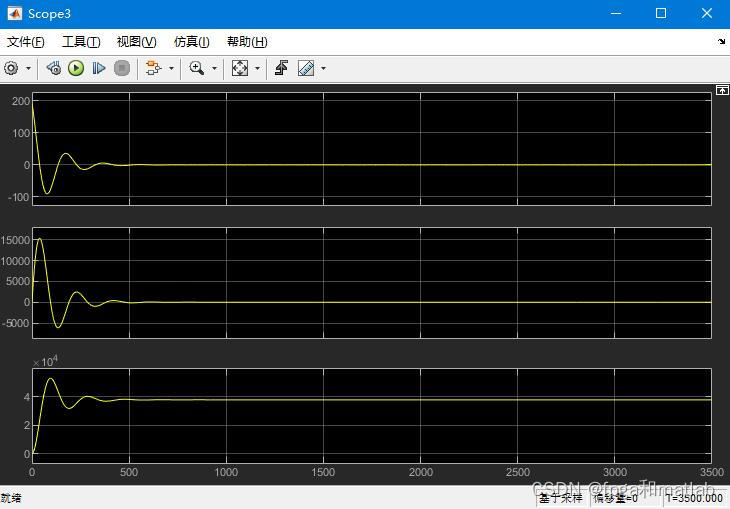

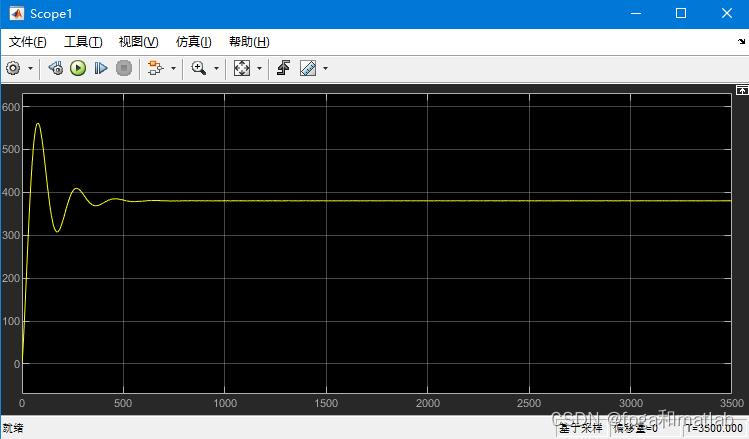

通过以上介绍,我们完成了模拟锁相环的基本构架,其仿真结果如下所示:

5266

5266

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?