一.亚稳态

1.亚稳态的产生原因

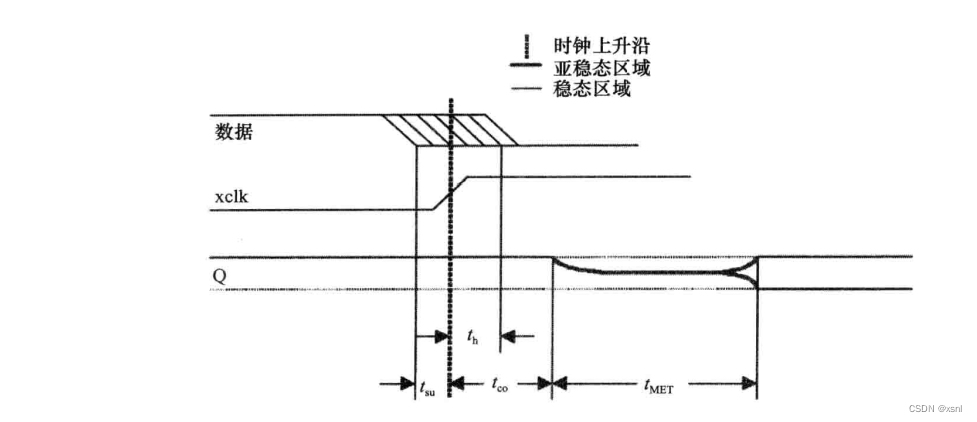

为了确保在时钟沿进行可靠稳定的操作,需要数据在时钟沿的前后稳定不变,时钟沿前数据应该保持不变的时间称为建立时间(Tsu),时钟沿后数据应该保持不变的时间称为保持时间(Th)。

信号在传输期间,不符合保持时间和建立时间的要求,寄存器输入端数据在对应时钟的保持时间和建立时间的时序窗口内变化,导致寄存器输出端处于一个不稳定的状态,如图一,然后此不稳定的状态逐级传递到其他寄存器,其他寄存器会采到不同的值,整个系统就会处于一种不一致的状态,逻辑混乱。

2.什么情况下会产生亚稳态?

(1)信号在不同时钟域进行传输,由于源时钟域和目的时钟域的相位不一样,导致源寄存器的输出会在任意的时间点到达目的寄存器,可能就会不满足建立时间和保持时间的要求。

(2)采集异步信号(例如异步复位电路的设计),由于异步信号会在任意时间到达目的寄存器,所以也可能会出现不满足建立时间和保持时间的要求。

二.CDC单bit信号处理

1.概述

按照上面产生亚稳态的两种情况可以分为,信号传输的跨时钟域处理以及采集异步信号的跨时钟域处理。信号传输的跨时钟域处理又可以分为单bit信号以及多bit信号传输的跨时钟域处

本文介绍了跨时钟域信号处理中的亚稳态问题及解决方案,包括不同情况下亚稳态产生的原因,以及针对单bit信号从慢时钟到快时钟、从快时钟到慢时钟的具体处理方法。

本文介绍了跨时钟域信号处理中的亚稳态问题及解决方案,包括不同情况下亚稳态产生的原因,以及针对单bit信号从慢时钟到快时钟、从快时钟到慢时钟的具体处理方法。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1240

1240

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?